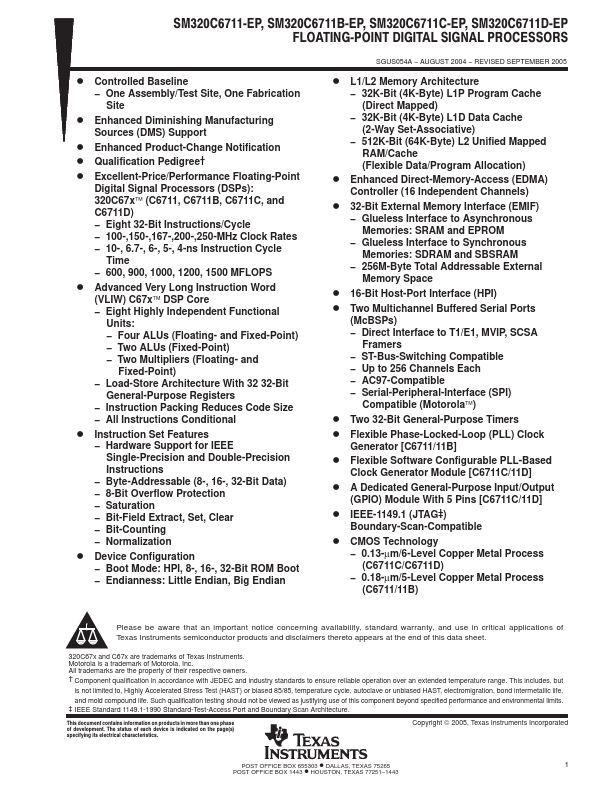

SM320C6711B-EP Overview

Key Features

- Hardware Support for IEEE Single-Precision and Double-Precision Instructions

- 8-Bit Overflow Protection

- Normalization D Device Configuration

- Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

- Endianness: Little Endian, Big Endian SGUS054A

- AUGUST 2004 - REVISED SEPTEMBER 2005 D L1/L2 Memory Architecture

- 32K-Bit (4K-Byte) L1P Program Cache (Direct Mapped)

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

- 256M-Byte Total Addressable External Memory Space D 16-Bit Host-Port Interface (HPI) D Two Multichannel Buffered Seri