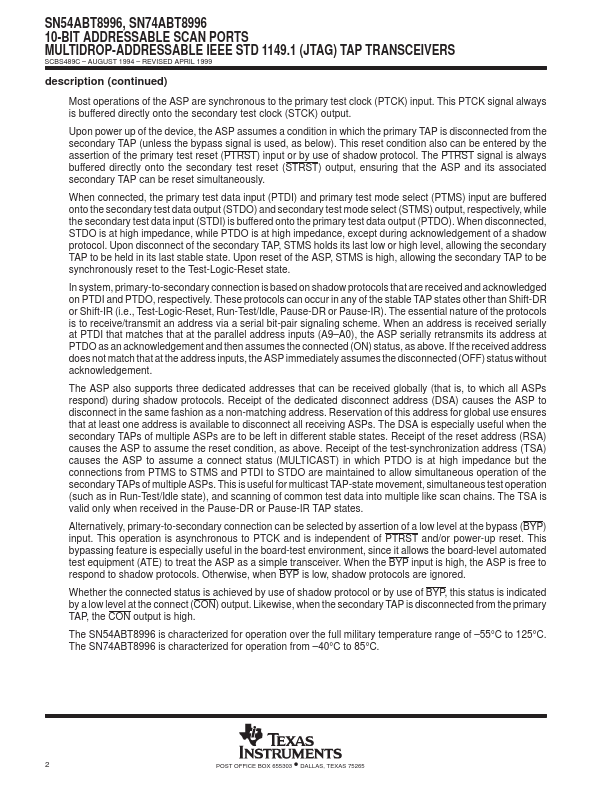

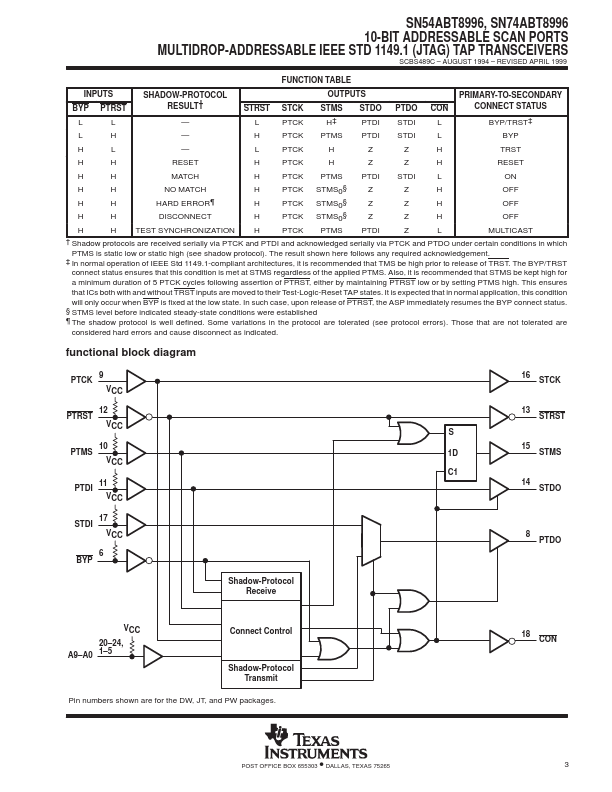

Datasheet Summary

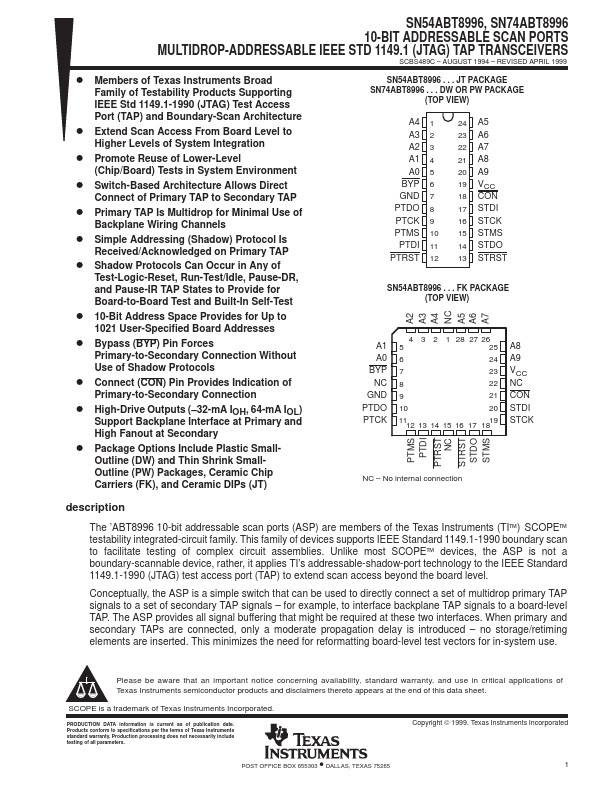

SN54ABT8996, SN74ABT8996

10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS

SCBS489C

- AUGUST 1994

- REVISED APRIL 1999

D Members of Texas Instruments Broad

Family of Testability Products Supporting

IEEE Std 1149.1-1990 (JTAG) Test Access

Port (TAP) and Boundary-Scan Architecture

D Extend Scan Access From Board Level to

Higher Levels of System Integration

D Promote Reuse of Lower-Level

(Chip/Board) Tests in System Environment

D Switch-Based Architecture Allows Direct

Connect of Primary TAP to Secondary TAP

D Primary TAP Is Multidrop for Minimal Use of

Backplane Wiring Channels

D Simple Addressing (Shadow) Protocol Is

Received/Acknowledged on...