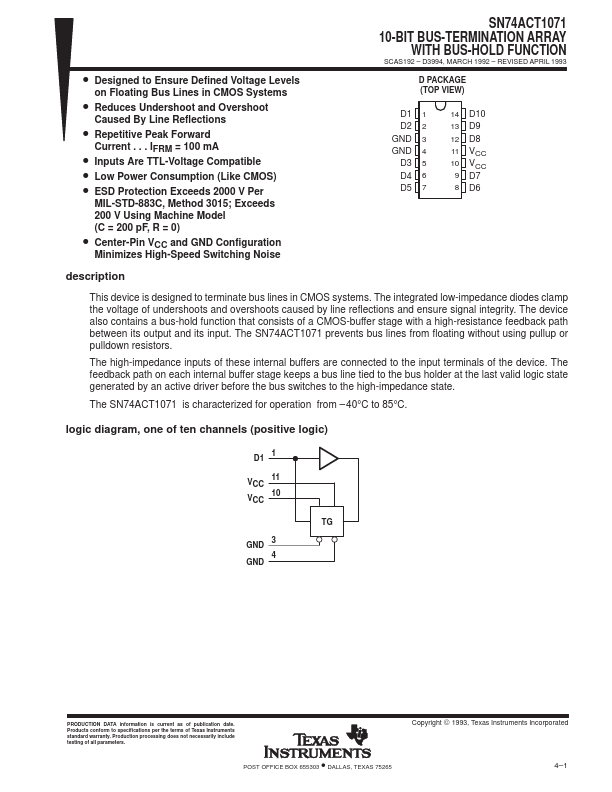

| Part | SN74ACT1071 |

|---|---|

| Description | 10-BIT BUS-TERMINATION ARRAY |

| Manufacturer | Texas Instruments |

| Size | 727.76 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CTA2P1N | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| CTA2N1P | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| 7003 | Allegro MicroSystems | HIGH-VOLTAGE/ HIGH-CURRENT DARLINGTON ARRAY |