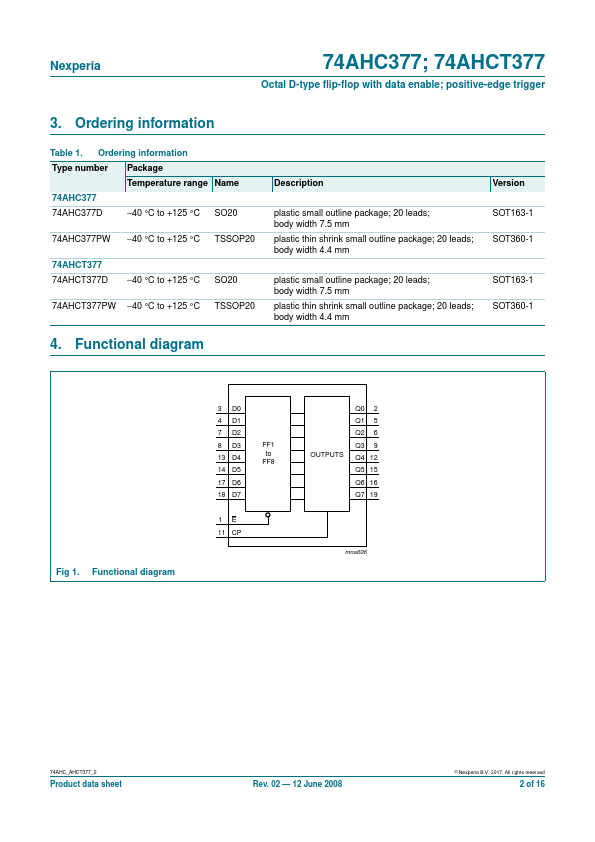

74AHCT377D Description

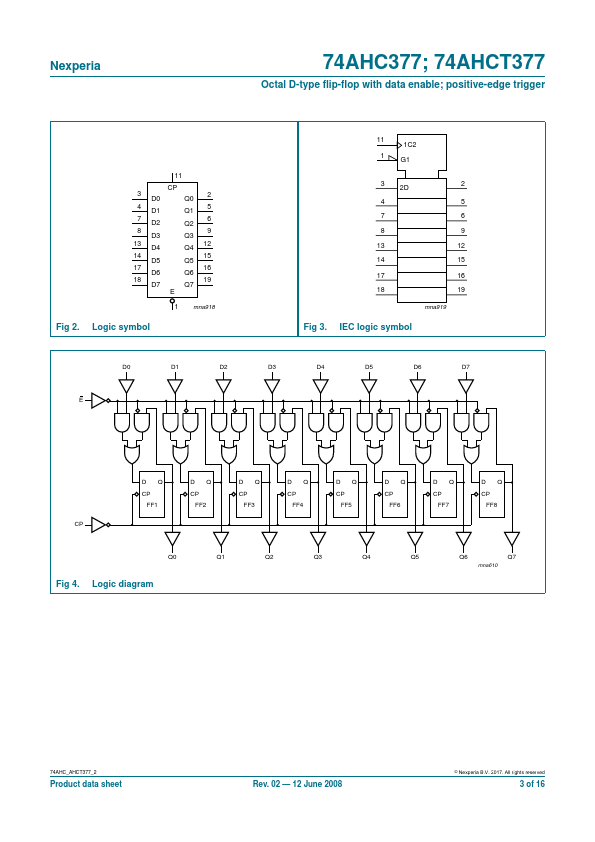

74AHCT377 is a high-speed Si-gate CMOS device and is pin patible with Low-power Schottky TTL (LSTTL). It is specified in pliance with JEDEC standard No. 74AHCT377 has eight edge-triggered, D-type flip-flops with individual D inputs and Q outputs.