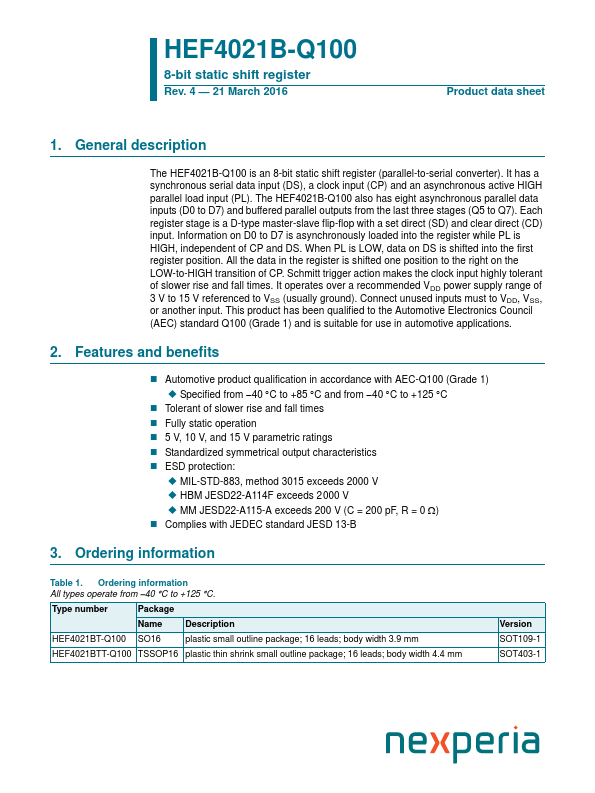

HEF4021B-Q100

Description

The HEF4021B-Q100 is an 8-bit static shift register (parallel-to-serial converter).

Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade 1) Specified from 40 C to +85 C and from 40 C to +125 C

- Tolerant of slower rise and fall times

- Fully static operation

- 5 V, 10 V, and 15 V parametric ratings

- Standardized symmetrical output characteristics

- ESD protection

- plies with JEDEC standard JESD 13-B