Description

MAX 7000 Programmable Logic Device Family Data Sheet

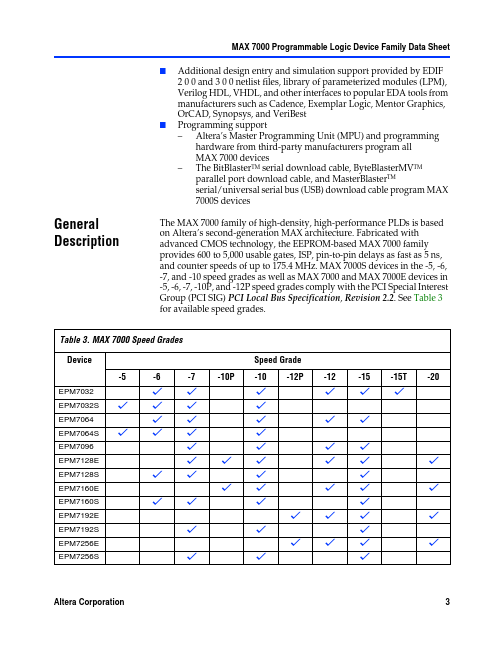

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest

Programming support

Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MA

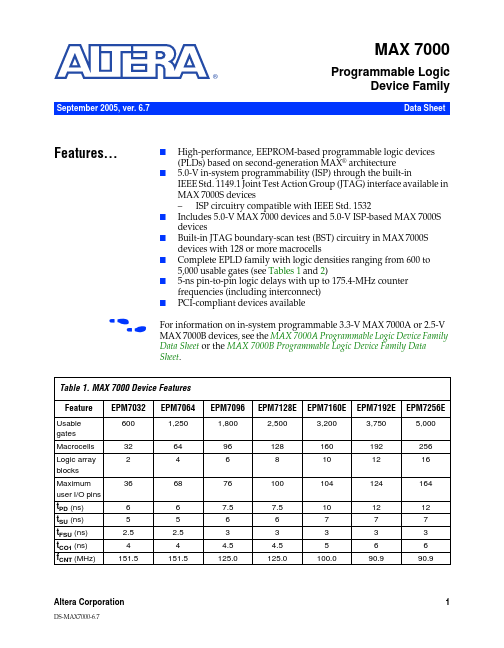

Features

- f.

- High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture.

- 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices.

- ISP circuitry compatible with IEEE Std. 1532.

- Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices.

- Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more mac.