Description

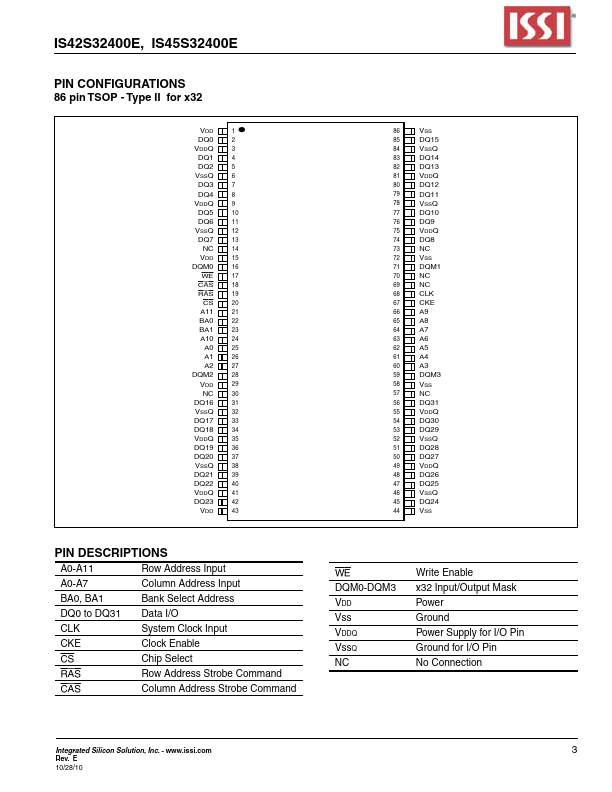

A0-A11

Row Address Input

A0-A7

Column Address Input

BA0, BA1

Bank Select Address

DQ0 to DQ31 Data I/O

CLK

System Clock Input

CKE

Clock Enable

CS

Chip Select

RAS

Row Address Strobe Command

CAS

Column Address Strobe Command

86 VSS 85 DQ15 84 VSSQ 83 DQ14 82 DQ13 81 VDDQ 80 DQ12 79 DQ11 78 VSSQ 77 DQ10 76 DQ9 75 VDDQ 74 DQ8 73 NC 72 VSS 71 DQM1 70 NC 69 NC 68 CLK 67 CKE 66 A9 65 A8 64 A7 63 A6 62 A5 61 A4 60 A3 59 DQM3 58 VSS 57 NC 56 DQ31 55 VDDQ 54 DQ30 5

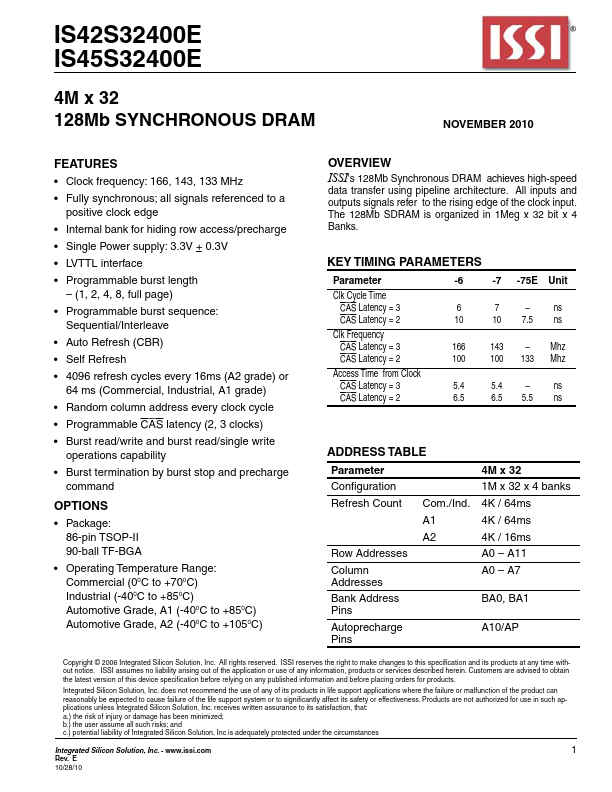

Features

- Clock frequency: 166, 143, 133 MHz.

- Fully synchronous; all signals referenced to a positive clock edge.

- Internal bank for hiding row access/precharge.

- Single Power supply: 3.3V + 0.3V.

- LVTTL interface.

- Programmable burst length.

- (1, 2, 4, 8, full page).

- Programmable burst sequence: Sequential/Interleave.

- Auto Refresh (CBR).

- Self Refresh.

- 4096 refresh cycles every 16ms (A2 grade) or 6.