IS62WV12816DBLL

Overview

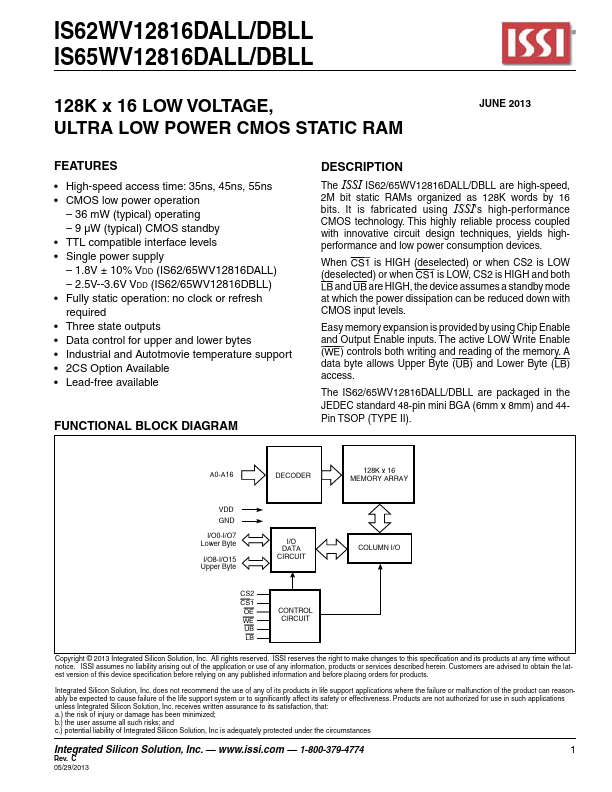

The ISSI IS62/65WV12816DALL/DBLL are high-speed, 2M bit static RAMs organized as 128K words by 16 bits. It is fabricated using ISSI's high-performance CMOS technology.

- High-speed access time: 35ns, 45ns, 55ns

- CMOS low power operation - 36 mW (typical) operating - 9 µW (typical) CMOS standby

- TTL compatible interface levels

- Single power supply - 1.8V ± 10% Vdd (IS62/65WV12816DALL) - 2.5V--3.6V Vdd (IS62/65WV12816DBLL)

- Fully static operation: no clock or refresh required

- Three state outputs

- Data control for upper and lower bytes

- Industrial and Autotmovie temperature support

- 2CS Option Available

- Lead-free available