Description

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

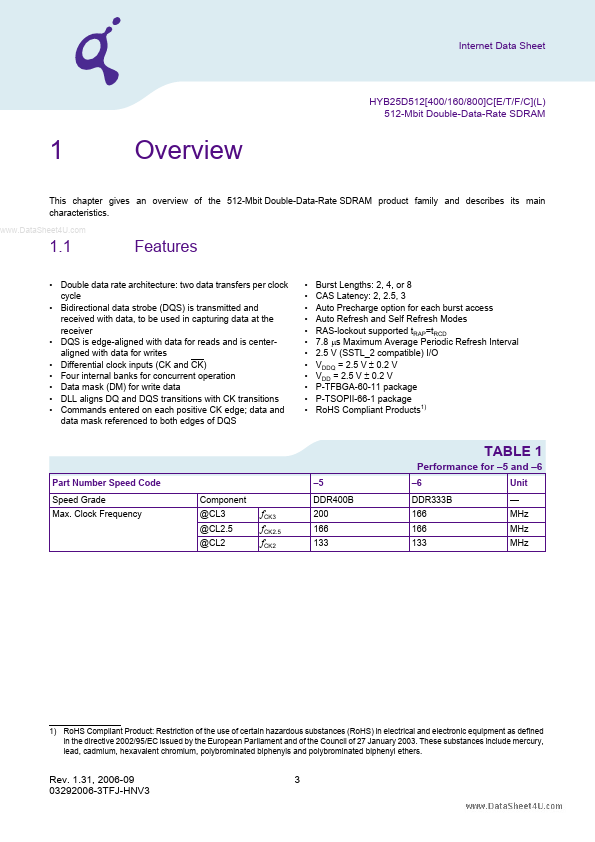

Features

- Burst Lengths: 2, 4, or 8 CAS Latency: 2, 2.5, 3 Auto Precharge option for each burst access Auto Refresh and Self Refresh Modes RAS-lockout supported tRAP=tRCD 7.8 µs Maximum Average Periodic Refresh Interval 2.5 V (SSTL_2 compatible) I/O VDDQ = 2.5 V ± 0.2 V VDD = 2.5 V ± 0.2 V P-TFBGA-60-11 package P-TSOPII-66-1 package RoHS Compliant Products1).

- Double data rate a.