Datasheet Details

- Part number

- K7J643682M, K7J641882M

- Manufacturer

- Samsung semiconductor

- File Size

- 361.01 KB

- Datasheet

- K7J641882M_Samsungsemiconductor.pdf

- Description

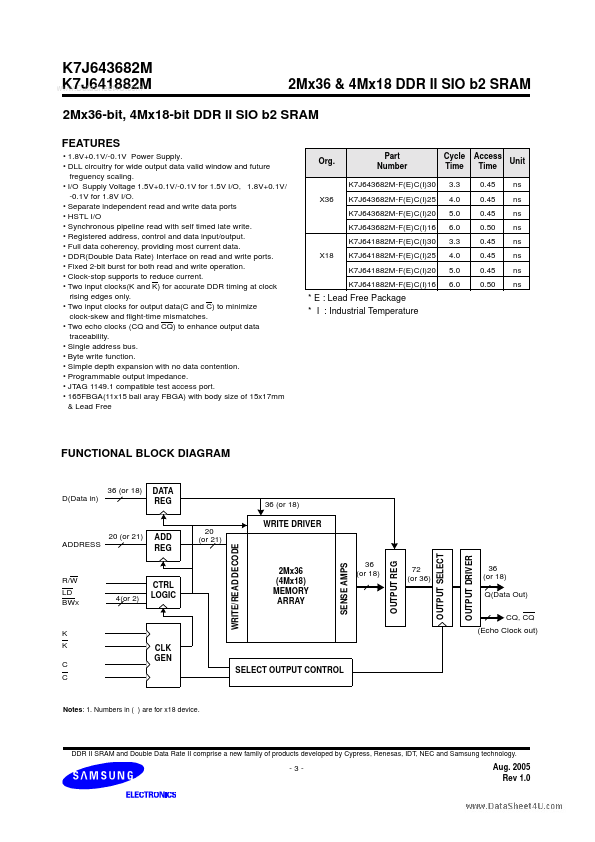

- (K7J641882M / K7J643682M) 72Mb M-die DDRII SRAM Specification

- Note

- This datasheet PDF includes multiple part numbers: K7J643682M, K7J641882M.

Please refer to the document for exact specifications by model.