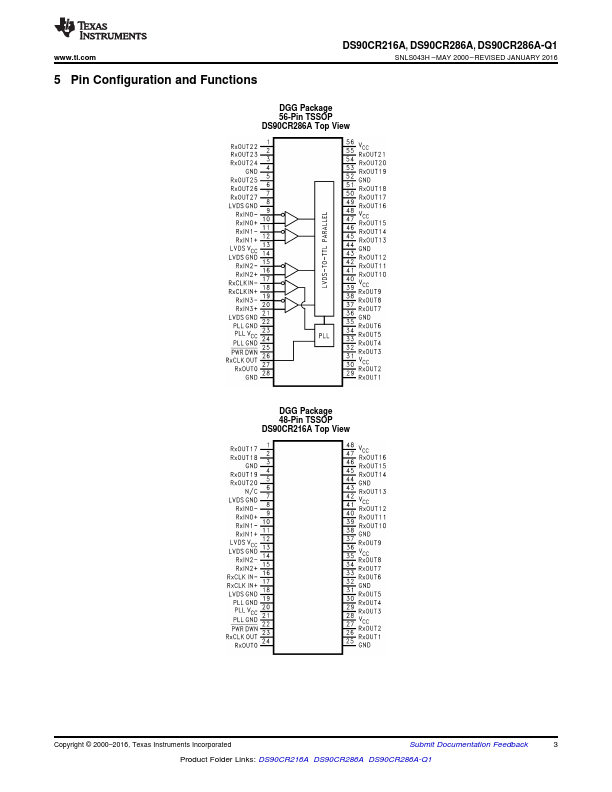

Description

The DS90CR286A receiver converts the four LVDS data streams back into parallel 28 bits of LVCMOS data.

Features

- 1 20 to 66 MHz Shift Clock Support.

- 50% Duty Cycle on Receiver Output Clock.

- Best.

- in.

- Class Set and Hold Times on Rx Outputs.

- Rx Power Consumption < 270 mW (Typ) at 66

MHz Worst Case.

- Rx Power-Down Mode < 200 μW (Max).

- ESD Rating > 7 kV (HBM), > 700 V (EIAJ).

- PLL Requires No External Components.

- Compatible with TIA/EIA-644 LVDS Standard.

- Low Profile 56-Pin or 48-Pin DGG (TSSOP)

Package.

- Opera.

DS90CR286A-etcTI.pdf

DS90CR286A-etcTI.pdf