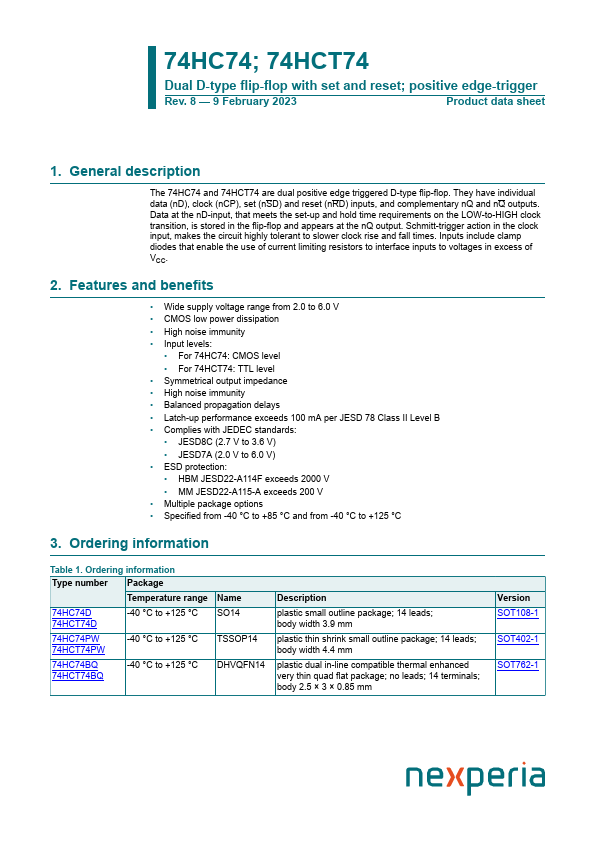

74HC74

description

The 74HC74 and 74HCT74 are dual positive edge triggered D-type flip-flop. They have individual data (n D), clock (n CP), set (n SD) and reset (n RD) inputs, and plementary n Q and n Q outputs. Data at the n D-input, that meets the set-up and hold time requirements on the LOW-to-HIGH clock transition, is stored in the flip-flop and appears at the n Q output. Schmitt-trigger action in the clock input, makes the circuit highly tolerant to slower clock rise and fall times. Inputs include clamp diodes that enable the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

- Wide supply voltage range from 2.0 to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Input levels:

- For 74HC74: CMOS level

- For 74HCT74: TTL level

- Symmetrical output impedance

- High noise immunity

- Balanced propagation delays

- Latch-up performance exceeds 100 m A per JESD 78 Class II Level B

- plies with JEDEC standards:

- JESD8C (2.7 V to 3.6...