AK5916384G

Description

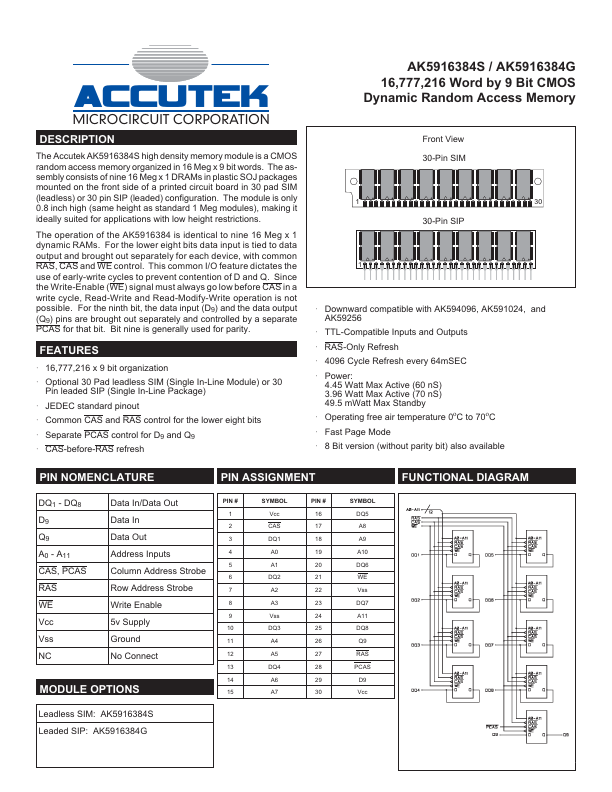

The Accutek AK5916384S high density memory module is a CMOS random access memory organized in 16 Meg x 9 bit words. The assembly consists of nine 16 Meg x 1 DRAMs in plastic SOJ packages mounted on the front side of a printed circuit board in 30 pad SIM (leadless) or 30 pin SIP (leaded) configuration.

Key Features

- Downward compatible with AK594096, AK591024, and AK59256

- TTL-Compatible Inputs and Outputs

- RAS-Only Refresh

- 4096 Cycle Refresh every 64mSEC

- Power: 4.45 Watt Max Active (60 nS) 3.96 Watt Max Active (70 nS) 49.5 mWatt Max Standby

- Operating free air temperature 0oC to 70oC

- Fast Page Mode

- 8 Bit version (without parity bit) also available FEATURES

- 16,777,216 x 9 bit organization

- Optional 30 Pad leadless SIM (Single In-Line Module) or 30 Pin leaded SIP (Single In-Line Package)