89C51CC01

Description

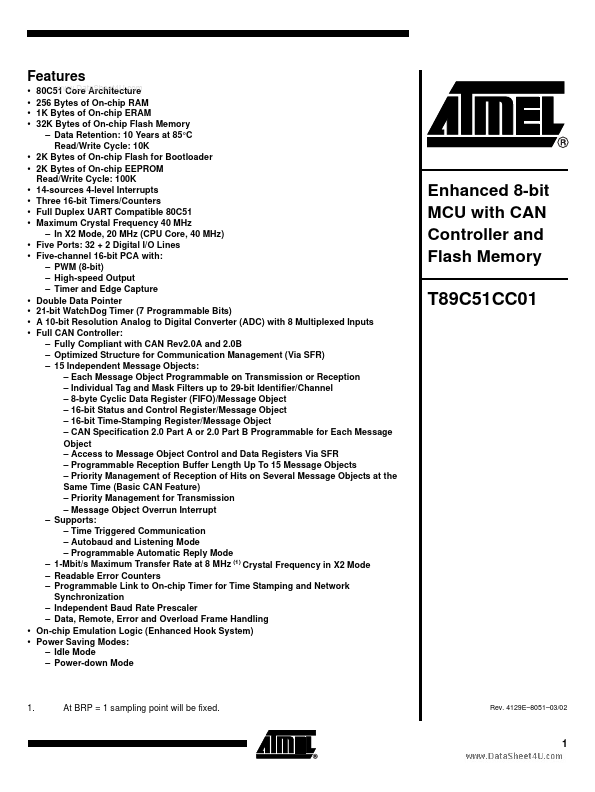

The T89C51CC01 is the first member of the CANaryTM family of 8-bit microcontrollers dedicated to CAN network applications. In X2 mode a maximum external clock rate of 20 MHz reaches a 300 ns cycle time.

Key Features

- T89C51CC01 * *

- At BRP = 1 sampling point will be fixed. Rev. 4129E-8051-03/02 1

- Power Supply: 5V ± 10% (or 3V (1) ± 10%)

- Packages: VQFP44, PLCC44, CA-BGA64