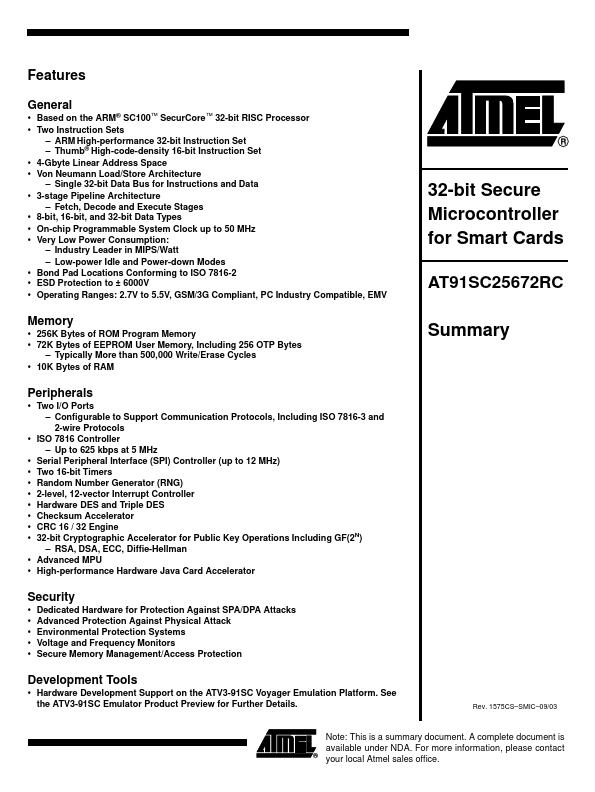

AT91SC25672RC

AT91SC25672RC is 32-bit Secure Microcontroller manufactured by Atmel.

Features

General

- Based on the ARM® SC100™ Secur Core™ 32-bit RISC Processor

- Two Instruction Sets

- -

- -

- -

- -

- - ARM High-performance 32-bit Instruction Set

- Thumb® High-code-density 16-bit Instruction Set 4-Gbyte Linear Address Space Von Neumann Load/Store Architecture

- Single 32-bit Data Bus for Instructions and Data 3-stage Pipeline Architecture

- Fetch, Decode and Execute Stages 8-bit, 16-bit, and 32-bit Data Types On-chip Programmable System Clock up to 50 MHz Very Low Power Consumption:

- Industry Leader in MIPS/Watt

- Low-power Idle and Power-down Modes Bond Pad Locations Conforming to ISO 7816-2 ESD Protection to ± 6000V Operating Ranges: 2.7V to 5.5V, GSM/3G pliant, PC Industry patible, EMV

32-bit Secure Microcontroller for Smart Cards

Memory

- 256K Bytes of ROM Program Memory

- 72K Bytes of EEPROM User Memory, Including 256 OTP Bytes

- Typically More than 500,000 Write/Erase Cycles

Summary

- 10K Bytes of RAM

Peripherals

- Two I/O Ports

- -

- -

- -

- -

- -

- - Configurable to Support munication Protocols, Including ISO 7816-3 and 2-wire Protocols ISO 7816 Controller

- Up to 625 kbps at 5 MHz Serial Peripheral Interface (SPI) Controller (up to 12 MHz) Two 16-bit Timers Random Number Generator (RNG) 2-level, 12-vector Interrupt Controller Hardware DES and Triple DES Checksum Accelerator CRC 16 / 32 Engine 32-bit Cryptographic Accelerator for Public Key Operations Including GF(2N)

- RSA, DSA, ECC, Diffie-Hellman Advanced MPU High-performance Hardware Java Card Accelerator

Security

- -

- -

- Dedicated Hardware for Protection Against SPA/DPA Attacks Advanced Protection Against Physical Attack Environmental Protection Systems Voltage and Frequency Monitors Secure Memory Management/Access Protection

Development Tools

- Hardware Development Support on the ATV3-91SC Voyager Emulation Platform. See the ATV3-91SC Emulator Product Preview for Further Details.

Rev. 1575CS- SMIC- 09/03

Note: This is a summary document. A plete document is 1...