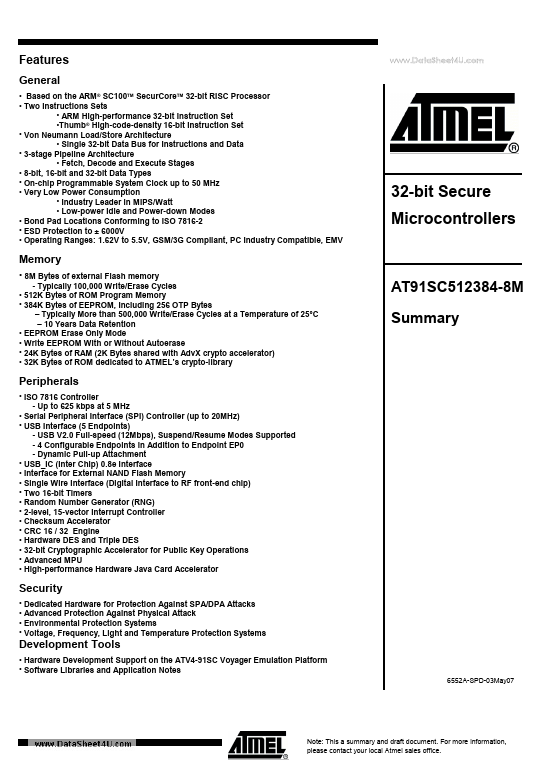

AT91SC512384-8M

AT91SC512384-8M is 32-bit Secure Microcontrollers manufactured by Atmel.

Features

General

- Based on the ARM® SC100TM Secur Core TM 32-bit RISC Processor

- Two Instructions Sets

- ARM High-performance 32-bit Instruction Set

- Thumb® High-code-density 16-bit Instruction Set

- Von Neumann Load/Store Architecture

- Single 32-bit Data Bus for Instructions and Data

- 3-stage Pipeline Architecture

- Fetch, Decode and Execute Stages

- 8-bit, 16-bit and 32-bit Data Types

- On-chip Programmable System Clock up to 50 MHz

- Very Low Power Consumption

- Industry Leader in MIPS/Watt

- Low-power Idle and Power-down Modes

- Bond Pad Locations Conforming to ISO 7816-2

- ESD Protection to ± 6000V

- Operating Ranges: 1.62V to 5.5V, GSM/3G pliant, PC Industry patible, EMV

..

32-bit Secure Microcontrollers

Memory

- 8M Bytes of external Flash memory

- Typically 100,000 Write/Erase Cycles

- 512K Bytes of ROM Program Memory

- 384K Bytes of EEPROM, Including 256 OTP Bytes

- Typically More than 500,000 Write/Erase Cycles at a Temperature of 25°C

- 10 Years Data Retention

- EEPROM Erase Only Mode

- Write EEPROM With or Without Autoerase

- 24K Bytes of RAM (2K Bytes shared with Adv X crypto accelerator)

- 32K Bytes of ROM dedicated to ATMEL’s crypto-library

AT91SC512384-8M Summary

Peripherals

- ISO 7816 Controller

- Up to 625 kbps at 5 MHz

- Serial Peripheral Interface (SPI) Controller (up to 20MHz)

- USB Interface (5 Endpoints)

- USB V2.0 Full-speed (12Mbps), Suspend/Resume Modes Supported

- 4 Configurable Endpoints in Addition to Endpoint EP0

- Dynamic Pull-up...