89C51CC01 Description

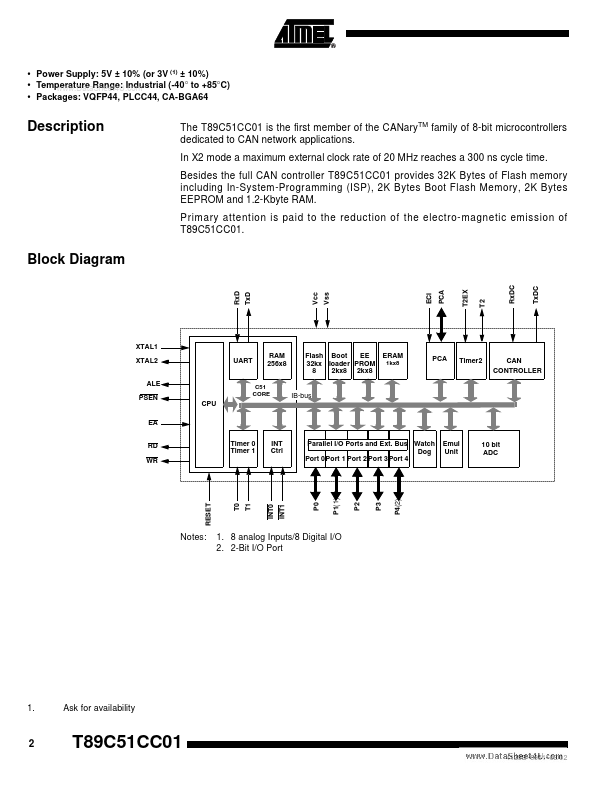

The T89C51CC01 is the first member of the CANaryTM family of 8-bit microcontrollers dedicated to CAN network applications. In X2 mode a maximum external clock rate of 20 MHz reaches a 300 ns cycle time. Besides the full CAN controller T89C51CC01 provides 32K Bytes of Flash memory including In-System-Programming (ISP), 2K Bytes Boot Flash Memory, 2K Bytes EEPROM and 1.2-Kbyte RAM.

89C51CC01 Key Features

- 80C51 Core Architecture 256 Bytes of On-chip RAM 1K Bytes of On-chip ERAM 32K Bytes of On-chip Flash Memory

- PWM (8-bit)

- High-speed Output

- Timer and Edge Capture Double Data Pointer 21-bit WatchDog Timer (7 Programmable Bits) A 10-bit Resolution Analog to Dig

- Fully pliant with CAN Rev2.0A and 2.0B

- Optimized Structure for munication Management (Via SFR)

- 15 Independent Message Objects

- Each Message Object Programmable on Transmission or Reception

- Individual Tag and Mask Filters up to 29-bit Identifier/Channel

- 8-byte Cyclic Data Register (FIFO)/Message Object