AS7C251MNTF36A

AS7C251MNTF36A is 2.5V 1M x 32/36 Flowthrough SRAM manufactured by Alliance Semiconductor Corporation.

- Part of the AS7C251MNTF32A comparator family.

- Part of the AS7C251MNTF32A comparator family.

Features

- -

- -

- -

- - Organization: 1,048,576 words × 32 or 36 bits NTD™architecture for efficient bus operation Fast clock to data access: 7.5/8.5/10 ns Fast OE access time: 3.5/4.0 ns Fully synchronous operation Flow-through mode Asynchronous output enable control Available in 100-pin TQFP package

- -

- -

- -

- Byte write enables Clock enable for operation hold Multiple chip enables for easy expansion 2.5V core power supply Self-timed write cycles Interleaved or linear burst modes Snooze mode for standby operation

..

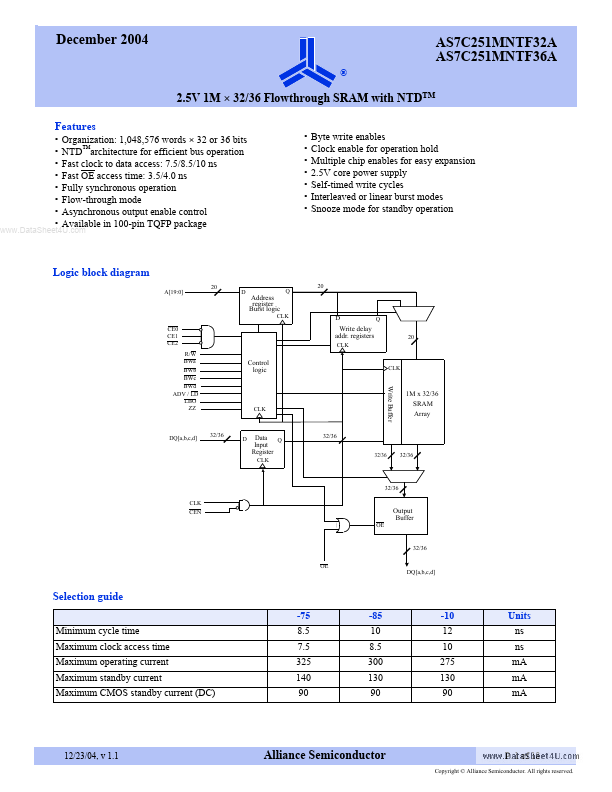

Logic block diagram

A[19:0] 20 D

Address register Burst logic

CLK CE0 CE1 CE2 R/W BWa BWb BWc BWd ADV / LD LBO ZZ

Q 20

Write delay addr. registers

Control logic

Write Buffer

1M x 32/36 SRAM Array

DQ[a,b,c,d]

32/36

Data Q Input Register

32/36 32/36 32/36

32/36 CLK CEN OE

Output Buffer

32/36 OE

DQ[a,b,c,d]

Selection guide

-75 Minimum cycle time Maximum clock access time Maximum operating current Maximum standby current Maximum CMOS standby current (DC) 8.5 7.5 325 140 90 -85 10 8.5 300 130 90 -10 12 10 275 130 90 Units ns ns m A m A m A

12/23/04, v 1.1

Alliance Semiconductor

P. 1 of 18

Copyright © Alliance Semiconductor. All rights...