AS7C33256PFS18B

AS7C33256PFS18B is 3.3V 256K X 18 pipeline burst synchronous SRAM manufactured by Alliance Semiconductor Corporation.

December 2004

®

3.3V 256K × 18 pipeline burst synchronous SRAM

Features

- -

- -

- -

- - Organization: 262,144 words × 18 bits Fast clock speeds to 200 MHz Fast clock to data access: 3.0/3.5/4.0 ns Fast OE access time: 3.0/3.5/4.0 ns Fully synchronous register-to-register operation Single-cycle deselect Asynchronous output enable control Available in 100-pin TQFP package

- -

- -

- -

- Individual byte write and global write Multiple chip enables for easy expansion Linear or interleaved burst control Snooze mode for reduced power-standby mon data inputs and data outputs 3.3V core power supply 2.5V or 3.3V I/O operation with separate VDDQ

..

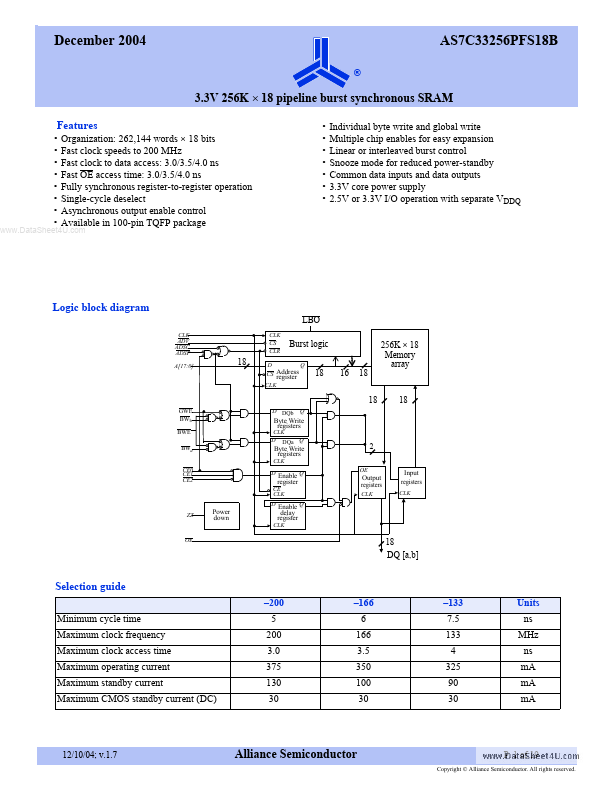

Logic block...