AS7C33512PFS32A

AS7C33512PFS32A is 3.3V 512K x 32/36 pipelined burst synchronous SRAM manufactured by Alliance Semiconductor Corporation.

Features

- -

- -

- -

- - Organization: 524,288 words × 32 or 36 bits Fast clock speeds to 166 MHz Fast clock to data access: 3.4/3.8 ns Fast OE access time: 3.4/3.8 ns Fully synchronous register-to-register operation Single-cycle deselect Asynchronous output enable control Available in 100-pin TQFP package

- -

- -

- -

- Individual byte write and global write Multiple chip enables for easy expansion 3.3V core power supply 2.5V or 3.3V I/O operation with separate VDDQ Linear or interleaved burst control Snooze mode for reduced power-standby mon data inputs and data outputs

..

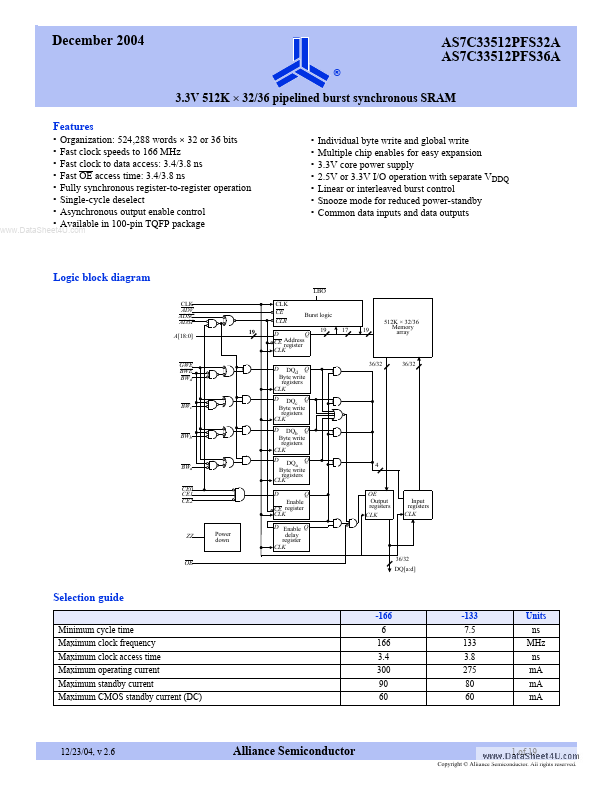

Logic block diagram

LBO CLK ADV ADSC ADSP A[18:0] 19 CLK CE CLR D CE Address register CLK D Q0 Burst logic Q1 19 Q

512K × 32/36 Memory array

GWE BWE BWd

DQd Q Byte write registers CLK D DQc Q Byte write registers CLK D DQb Q Byte write registers CLK D DQa Q Byte write registers CLK D Enable CE register CLK Power down D Enable Q delay register CLK Q

36/32

36/32

BWc

BWb

BWa CE0 CE1 CE2

OE Output registers CLK

Input registers CLK

36/32 DQ[a:d]

Selection guide

Minimum cycle time Maximum clock frequency Maximum clock access time Maximum operating current Maximum standby current Maximum CMOS standby current (DC) -166 6 166 3.4 300 90 60 -133 7.5 133 3.8 275 80 60 Units ns MHz ns m A m A m A

12/23/04, v 2.6

Alliance Semiconductor

1 of 19

Copyright © Alliance Semiconductor. All rights reserved.

AS7C33512PFS32A AS7C33512PFS36A

®

16 Mb Synchronous SRAM products list1,2

Org 1MX18 512KX32 512KX36 1MX18 512KX32 512KX36 1MX18 .. 512KX32 512KX36 1MX18 512KX32 512KX36 1MX18 512KX32 512KX36 Part Number AS7C331MPFS18A AS7C33512PFS32A AS7C33512PFS36A AS7C331MPFD18A AS7C33512PFD32A AS7C33512PFD36A AS7C331MFT18A AS7C33512FT32A AS7C33512FT36A AS7C331MNTD18A AS7C33512NTD32A AS7C33512NTD36A AS7C331MNTF18A AS7C33512NTF32A AS7C33512NTF36A Mode PL-SCD PL-SCD PL-SCD PL-DCD PL-DCD PL-DCD FT FT FT NTD-PL NTD-PL NTD-PL NTD-FT NTD-FT NTD-FT Speed 166/133 MHz 166/133 MHz 166/133 MHz 166/133...