| Part | AD9520-2 |

|---|---|

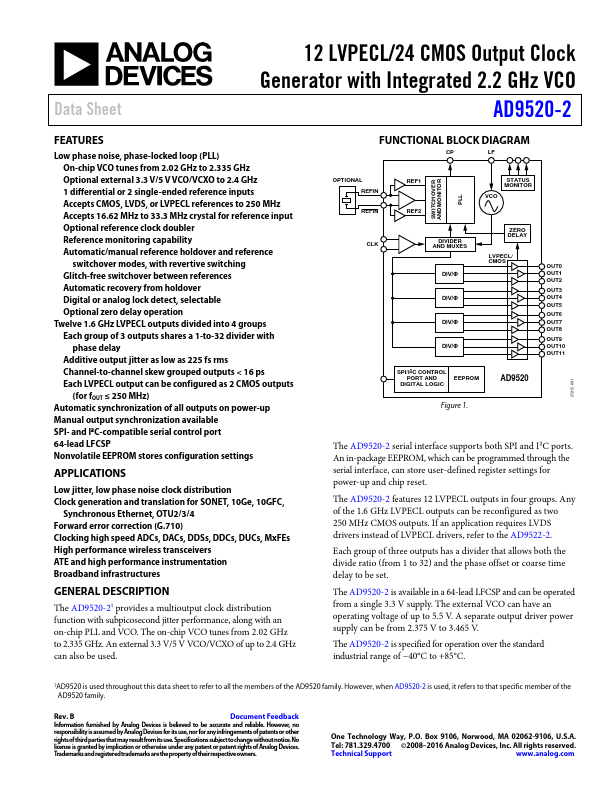

| Description | 12 LVPECL/24 CMOS Output Clock Generator |

| Manufacturer | Analog Devices |

| Size | 1.37 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| XR2206 | Exar | Monolithic Function Generator |

| AN97 | Maxim Integrated | Telephone Tone Generator |

| AN97 | Maxim Integrated | Telephone Tone Generator Requires No trimming |