AS5SP1M36DQ

AS5SP1M36DQ is 36Mb Pipelined Sync SRAM manufactured by Austin Semiconductor.

AUSTIN SEMICONDUCTOR, INC. Austin Semiconductor, Inc. 36Mb Pipelined Sync SRAM

Features

- Supports bus operation up to 200 MHz

- Available speed grades are 200 and 166 MHz

- Registered inputs and outputs for pipelined operation

- 3.3V core power supply

- 2.5V/3.3V I/O power supply

- Fast clock-to-output times

- Provide high-performance 3-1-1-1 access rate

- User-selectable burst counter supporting Intel®

- Pentium® interleaved or linear burst sequences

- Separate processor and controller address strobes

- Synchronous self-timed writes

- Asynchronous output enable

- Single Cycle Chip Deselect

- Available in lead-free 100-pin TQFP package

- IEEE 1149.1 JTAG-patible Boundary Scan

- “ZZ” Sleep Mode Option OPTION MARKING

/XT /IT /ET Temperature Range Military Temp (-55o C to +125o C) Industrial (-40o C to +85o C) Enhanced (-40o C to +105o C)

SSRAM

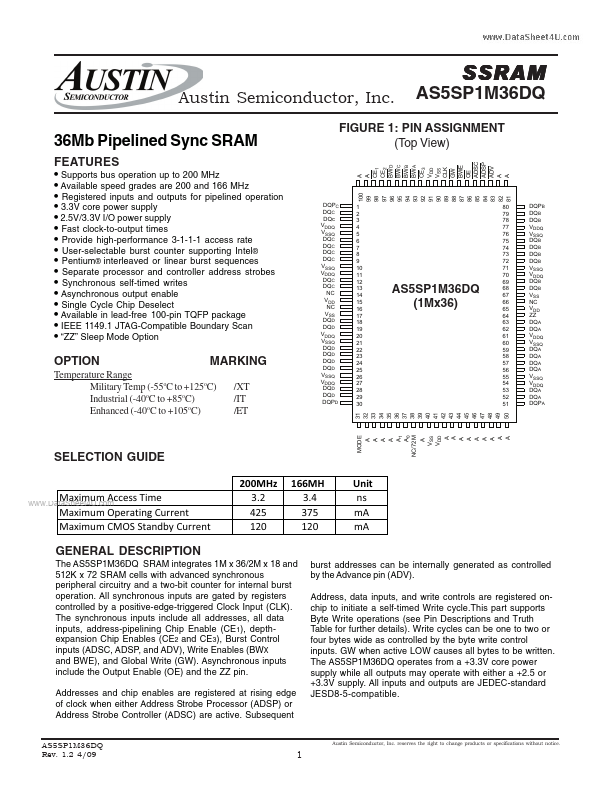

FIGURE 1: PIN ASSIGNMENT (Top View)

A A CE1 CE2 BWD BWC BWB BWA CE3 VDD VSS CLK GW BWE OE ADSC ADSP ADV A A

DQPC DQC DQc VDDQ VSSQ DQC DQC DQC DQC VSSQ VDDQ DQC DQC NC VDD NC VSS DQD DQD VDDQ VSSQ DQD DQD DQD DQD VSSQ VDDQ DQD DQD DQPD

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

AS5SP1M36DQ CY7C1440AV33 (1Mx36)

(1M x 36)

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

DQPB DQB DQB VDDQ VSSQ DQB DQB DQB DQB VSSQ VDDQ DQB DQB VSS NC VDD ZZ DQA DQA VDDQ VSSQ DQA DQA DQA DQA VSSQ VDDQ DQA DQA DQPA

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 MODE A A A A A1 A0 NC/72M A VSS...