CAT28F002

CAT28F002 is 2 Megabit CMOS Boot Block Flash Memory manufactured by Catalyst Semiconductor.

FEATURES s Fast Read Access Time: 90/120/150 ns s On-Chip Address and Data Latches s Blocked Architecture: s Electronic Signature

Licensed Intel second source s 100,000 Program/Erase Cycles and 10 Year

Data Retention s Standard Pinouts:

- One 16-KB Protected Boot Block

- Top or Bottom Locations

- Two 8-KB Parameter Blocks

- One 96-KB Main Block

- One 128-KB Main Block s Hardware Data Protection s Automated Program and Erase Algorithms s Automatic Power Savings Feature s Low Power CMOS Operation s 12.0V

- 40-Lead TSOP

- 40-Lead PDIP s High Speed Programming s mercial, Industrial and Automotive Tem- perature Ranges s Reset/Deep Power Down Mode

- 0.2µA ICC Typical

- Acts as Reset for Boot Operations

± 5% Programming and Erase Voltage

DESCRIPTION

The CAT28F002 is a high speed 256K X 8-bit electrically erasable and reprogrammable Flash memory ideally suited for applications requiring in-system or after sale code updates. The CAT28F002 has a blocked architecture with one 16 KB Boot Block, two 8 KB Parameter Blocks, one 96 KB Main Block and one 128 KB Main Block. The Boot Block section can be at the top or bottom of the memory map. The Boot Block section includes a reprogramming write lock out feature to guarantee data integrity. It is designed to contain secure code which will bring up the system minimally and download code to other locations of CAT28F002. The CAT28F002 is designed with a signature mode which allows the user to identify the IC manufacturer and device type. The CAT28F002 is also designed with on Chip Address Latches, Data Latches, Programming and Erase Algorithms. A deep power-down mode lowers the total Vcc power consumption 1µw typical. The CAT28F002 is manufactured using Catalyst’s advanced CMOS floating gate technology. It is designed to endure 100,000 program/erase cycles and has a data retention of 10 years. The device is available in JEDEC approved 40-pin TSOP and 40-pin PDIP packages.

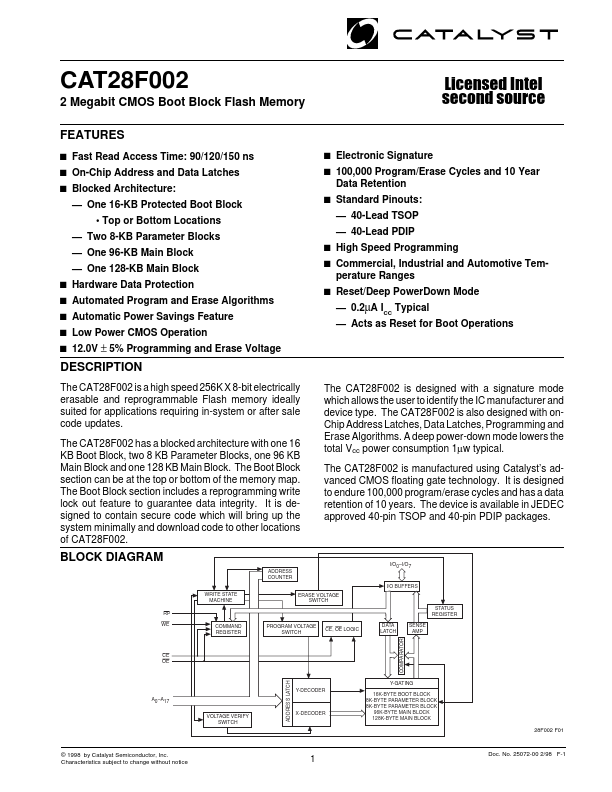

BLOCK DIAGRAM

ADDRESS COUNTER WRITE STATE MACHINE RP WE...