CS2501

CS2501 is Fractional-N Clock Multiplier manufactured by Cirrus Logic.

Features

- I²C/SPI control port

- Fractional clock multiplier and jitter reduction using hybrid analog/digital PLL

- Generates low-jitter 6- 75 MHz clock (CLK_OUT), synchronized to a 50 Hz- 30 MHz low-quality or intermittent frequency reference (CLK_IN)

- Flexible timing reference source

- External clock, external crystal, or built-in oscillator

- Configurable auxiliary clock/status output

- Minimal board space required

- No external analog loop-filter ponents

- Pin-to-pin, register map, and control patible with CS2100 and CS2300

- Single-supply operation at 1.8 V or 3.3 V

- High resolution PLL ratio (1 PPM)

- 40 ps RMS period jitter (external timing reference), 35 ps RMS period jitter (oscillator reference)

- Glitchless clock output generated from intermittent input

Applications

- Automotive audio systems

- Digital audio systems

- Network and USB audio interfaces

- Io T sensor and transducer systems

- Embedded systems

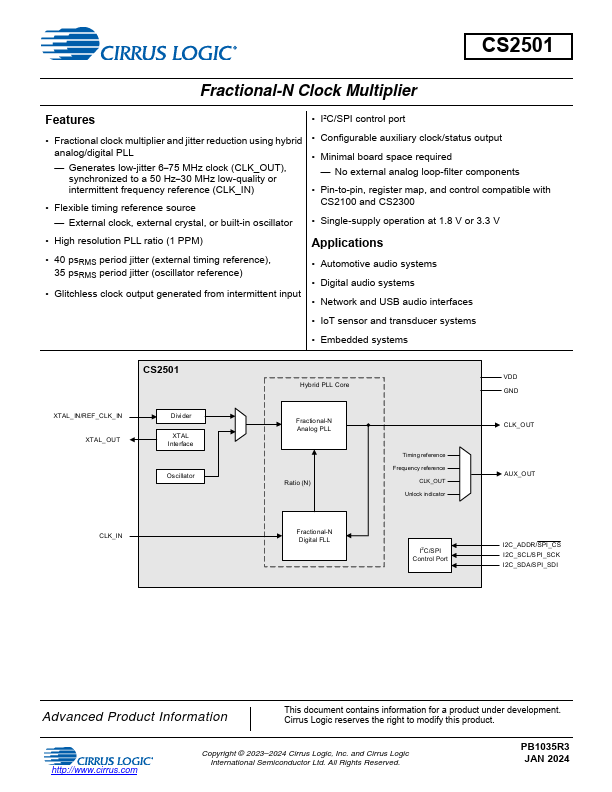

XTAL_ IN/REF_CLK_ IN XTAL_ OUT

Divi der XTAL Inte rface

Oscillator

Hyb rid PLL Core Fractio nal-N Ana log PLL

Ratio (N)

Timing ref erence Frequency reference

CLK _OUT Unlock indicator

VDD GND CLK_O UT

AUX_O UT

CLK_IN

Fractio nal-N Digital FLL

I2C/S PI Control Port

I2C_ADDR/SPI_CS I2C_SCL/S PI_SCK I2C_SDA/S PI_SDI

Advanced Product Information

This document contains information for a product under development. Cirrus Logic reserves the right to modify this product. http://.cirrus.

Copyright © 2023- 2024 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd. All Rights Reserved.

PB1035R3 JAN 2024

General Description

The CS2501 is a system-clocking device incorporating a programmable phase-locked loop (PLL). The hybrid analog/ digital PLL architecture prises a delta-sigma fractional-N analog PLL and a digital frequency-locked loop (FLL). The CS2501 enables clock generation from a stable timing reference clock. The device can generate low-jitter clocks from a noisy clock reference at frequencies as low as 50...