CY28352

CY28352 is Differential Clock Buffer/Driver manufactured by Cypress.

Features

- Supports 333-MHz and 400-MHz DDR SDRAM

- 60-

- 200-MHz operating frequency

- Phase-locked loop (PLL) clock distribution for double data rate synchronous DRAM applications

- Distributes one clock input to six differential outputs

- External feedback pin FBIN is used to synchronize output to clock input

- Conforms to DDRI specification

- Spread Aware™ for electromagnetic interference (EMI) reduction

- 28-pin SSOP package

Description

This PLL clock buffer is designed for 2.5-VDD and 2.5-AVDD operation and differential output levels. This device is a zero delay buffer that distributes a clock input CLKIN to six differential pairs of clock outputs (CLKT[0:5], CLKC[0:5]) and one feedback clock output FBOUT. The clock outputs are controlled by the input clock CLKIN and the feedback clock FBIN. The two-line serial bus can set each output clock pair (CLKT[0:5], CLKC[0:5]) to the Hi-Z state. When AVDD is grounded, the PLL is turned off and bypassed for test purposes. The PLL in this device uses the input clock CLKIN and the feedback clock FBIN to provide high-performance, low-skew, low- jitter output differential clocks.

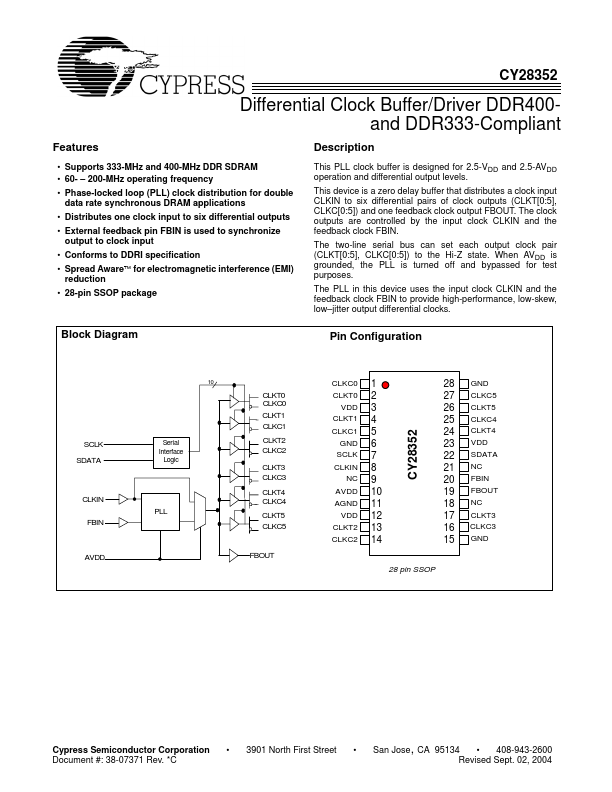

Block Diagram

Pin Configuration

SCLK SDATA

Serial Interface Logic

CLKT2 CLKC2 CLKT3 CLKC3

CLKIN NC AVDD AGND VDD CLKT2 CLKC2

CLKT0 CLKC0 CLKT1 CLKC1

CLKC0 CLKT0 VDD CLKT1 CLKC1 GND SCLK

CLKIN PLL FBIN

CLKT4 CLKC4 CLKT5 CLKC5

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16 15

GND CLKC5 CLKT5 CLKC4 CLKT4 VDD SDATA NC FBIN FBOUT NC CLKT3 CLKC3 GND

AVDD

FBOUT

28 pin SSOP

Cypress Semiconductor Corporation Document #: 38-07371 Rev.

- C

- 3901 North First Street

- San Jose, CA 95134

- 408-943-2600 Revised Sept. 02, 2004

Pin Description

[1]

Pin Number Pin Name 8 CLKIN 20 FBIN I/O I I O O O I I/O Pin Description plementary Clock Input. Feedback Clock Input. Connect to FBOUT for accessing the PLL. Clock Outputs Clock Outputs Feedback Clock Output. Connect to FBIN for normal operation. A bypass...