CY29976

CY29976 is Multi-Output Zero Delay Buffer manufactured by Cypress.

3.3V, 125-MHz, Multi-Output Zero Delay Buffer

Features

- -

- -

- -

Output frequency up to 125 MHz Supports Power PC , and Pentium processors 12 clock outputs: frequency configurable Configurable Output Disable Two reference clock inputs for dynamic toggling Oscillator or PECL reference input

® ®

- -

- -

- -

Spread spectrum patible Glitch-free output clocks transitioning 3.3V power supply Pin patible with SC973X Industrial temperature range:

- 40°C to +85°C 52-Pin TQFP package

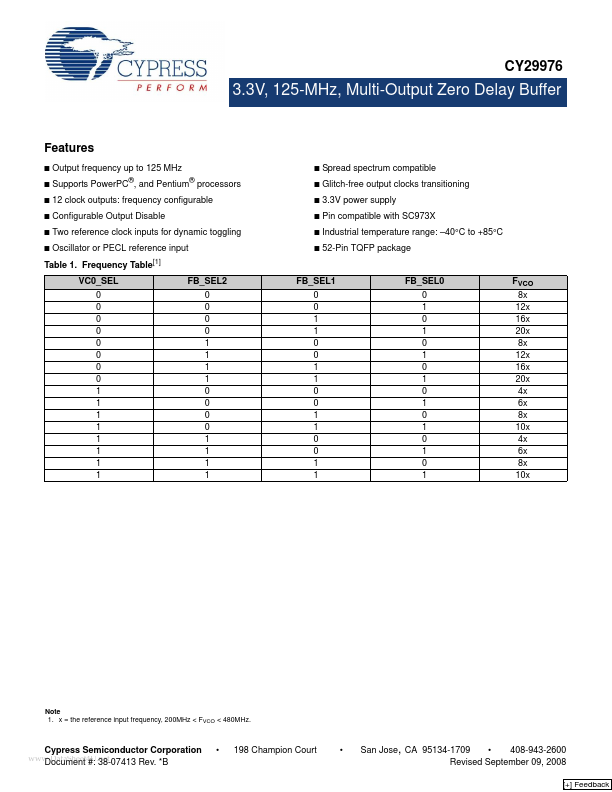

Table 1. Frequency Table[1] VC0_SEL 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 FB_SEL2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 FB_SEL1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 FB_SEL0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 FVCO 8x 12x 16x 20x 8x 12x 16x 20x 4x 6x 8x 10x 4x 6x 8x 10x

Note 1. x = the reference input frequency, 200MHz < FVCO < 480MHz.

..net

Cypress Semiconductor Corporation Document #: 38-07413 Rev.

- B

- 198 Champion Court

- San Jose, CA 95134-1709

- 408-943-2600 Revised September 09, 2008

[+] Feedback

Logic Block Diagram

P E C L P E C L_ V C O P L R E F _C LK C LK # _S E L L_E N _S E L D T C LK 0 T C LK 1 T C LK _S E L F B _ IN D Q S ync F rz 0 1 P hase D e te c to r LP F V C O 0 1 Q S ync F rz Q A 0 Q A 1 Q A 2 Q A 3 Q B 0 Q B 1 Q B 2 Q B 3

M R # /O E P o w e r-O n R eset S E L A (0 ,1 ) S E L B (0 ,1 ) S E L C (0 ,1 ) F B _ S E L (0 :2 ) S C LK S D A T A IN V _ C L K O u tp u t D is a b le C ir c u itr y 12 2 2 2 3 /4 , /6 , /8 , /1 0 S y n c P u ls e D a ta G e n e ra to r D Q D Q D /2 , /6 , /4 , /1 2 /2 , /6 , /4 , /1 0 /8 , /2 , /6 , /4 D Q Q

S ync F rz

Q C 0 Q C 1

S ync F rz S ync F rz S ync F rz

Q C 2 Q C 3 F B _O U T

Pinouts

VCO_SEL SELA0 SELA1 SELB0 SELB1 VDDC VDDC QA0 QA1 QA2 QA3 VSS...