CY29942

CY29942 is 1:18 Clock Distribution Buffer manufactured by Cypress.

2.5V or 3.3V, 200-MHz, 1:18 Clock Distribution Buffer

Features

- -

- -

- -

- -

- - 200-MHz clock support 2.5V or 3.3V operation LVCMOS/LVTTL clock input LVCMOS-/LVTTL-patible inputs 18 clock outputs: drive up to 36 clock lines 200 ps max. output-to-output skew Output Enable control Pin patible with MPC942C Available in Industrial and mercial 32-pin LQFP package

Description

The CY29942 is a low-voltage 200-MHz clock distribution buffer with an LVCMOS or LVTTL patible input clock. All other control inputs are LVCMOS/LVTTL patible. The eighteen outputs are 2.5V or 3.3V LVCMOS or LVTTL patible and can drive 50 Ω series or parallel terminated transmission lines. For series terminated transmission lines, each output can drive one or two traces giving the devices an effective fanout of 1:36. Low output-to-output skews make the CY29942 an ideal clock distribution buffer for nested clock trees in the most demanding of synchronous systems.

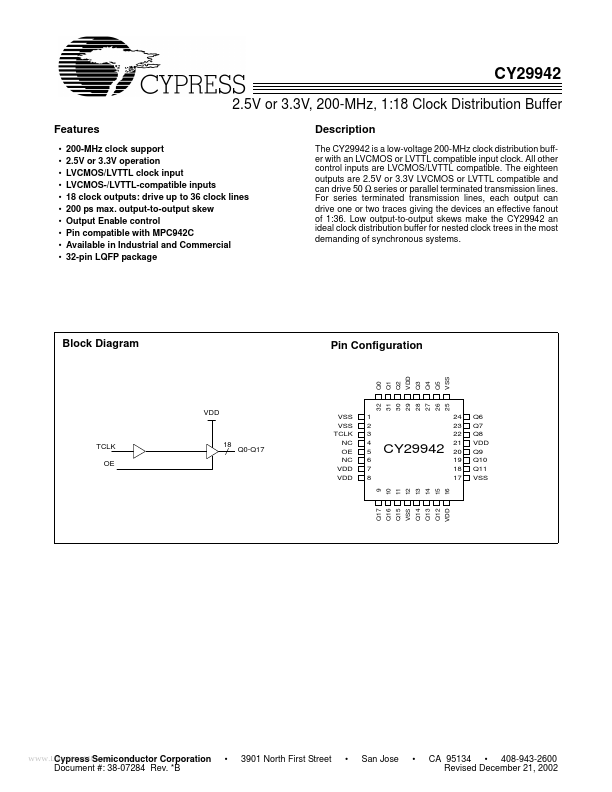

Block Diagram

Pin Configuration

VDD VSS 25 24 23 22 21 20 19 18 17 16

Q0

Q1

Q2

Q3 28

Q4 27

TCLK OE

Q0-Q17

VSS VSS TCLK NC OE NC VDD VDD

1 2 3 4 5 6 7 8 9

Q5

Q6 Q7 Q8 VDD Q9 Q10 Q11 VSS

13 Q14

14 Q13

Q17

Q16

Q15

Q12

..net Cypress Semiconductor...