Datasheet Summary

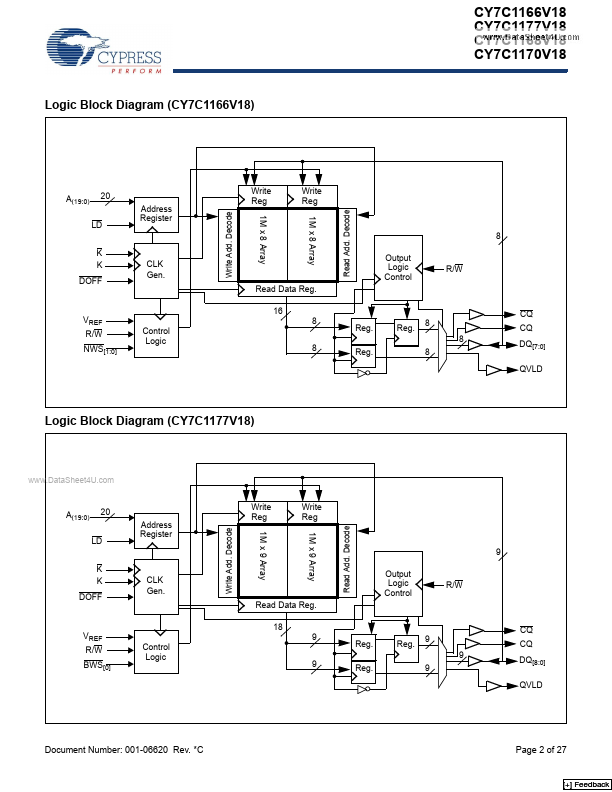

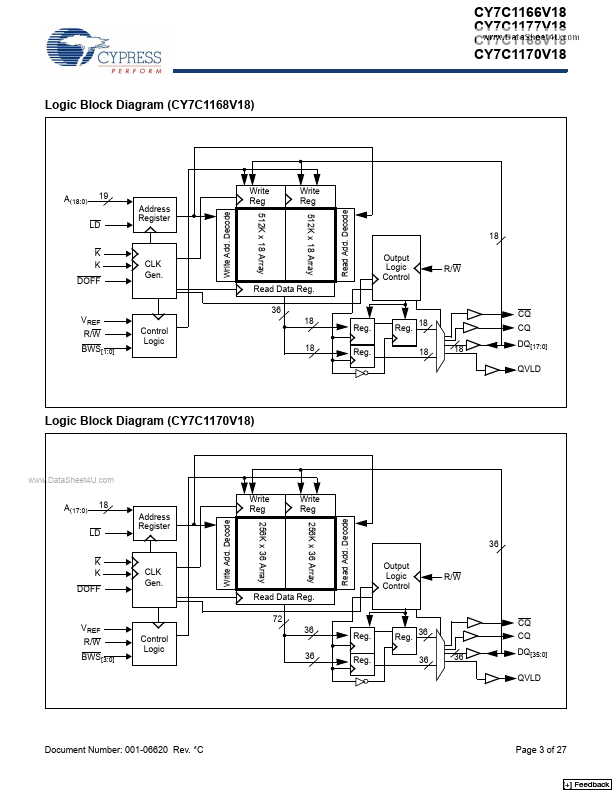

CY7C1166V18 CY7C1177V18 CY7C1168V18 CY7C1170V18

18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency)

Features

- -

- -

- -

Functional Description

The CY7C1166V18, CY7C1177V18, CY7C1168V18, and CY7C1170V18 are 1.8V Synchronous Pipelined SRAMs equipped with DDR-II+ architecture. The DDR-II+ consists of an SRAM core with an advanced synchronous peripheral circuitry. Addresses for read and write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K and K. Read data is driven on the rising edges of K and K. Each address location is associated with two 8-bit words (CY7C1166V18), or 9-bit words (CY7C1177V18), or...