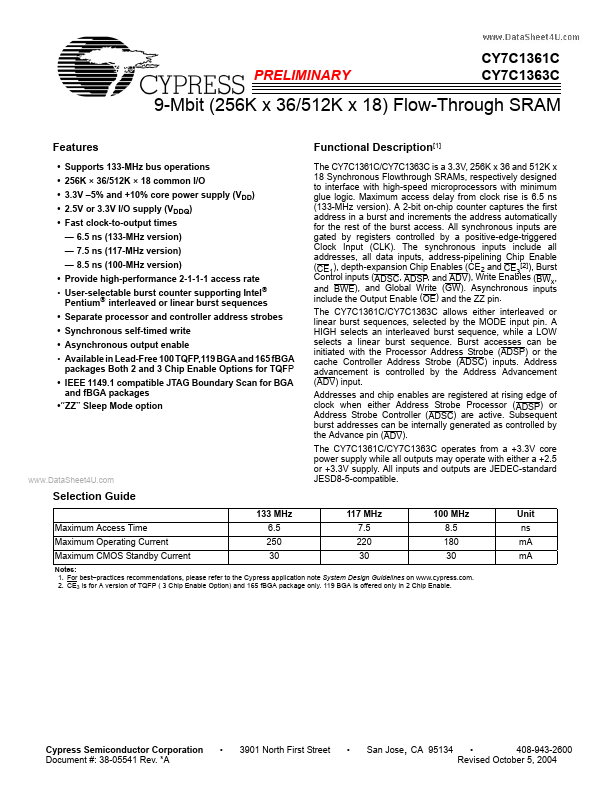

| Part | CY7C1363C |

|---|---|

| Description | 9-Mbit (256K x 36/512K x 18) Flow-Through SRAM |

| Manufacturer | Cypress |

| Size | 531.24 KB |

Pricing from 12.31125 USD, available from Avnet and Rochester Electronics.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Avnet | 39 | 59+ : 12.31125 USD 118+ : 11.16365 USD 236+ : 10.99328 USD 472+ : 10.84419 USD |

View Offer |

| Rochester Electronics | 1250 | 25+ : 10.58 USD 100+ : 10.05 USD 500+ : 9.52 USD 1000+ : 8.99 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CY7C136AE | Cypress | 1K/2K x 8 Dual-Port Static RAM |

| CY7C136E | Cypress | 1K/2K x 8 Dual-Port Static RAM |