Datasheet Summary

CY7C1410JV18, CY7C1425JV18 CY7C1412JV18, CY7C1414JV18

36-Mbit QDR™-II SRAM 2-Word Burst Architecture

Features

- Configurations

- 4M x 8 CY7C1425JV18

- 4M x 9 CY7C1412JV18

- 2M x 18 CY7C1414JV18

- 1M x 36

Separate independent read and write data ports

- Supports concurrent transactions 267 MHz clock for high bandwidth 2-word burst on all accesses (data transferred at 534 MHz) at 267 MHz

- -

- Double Data Rate (DDR) interfaces on both read and write ports ..

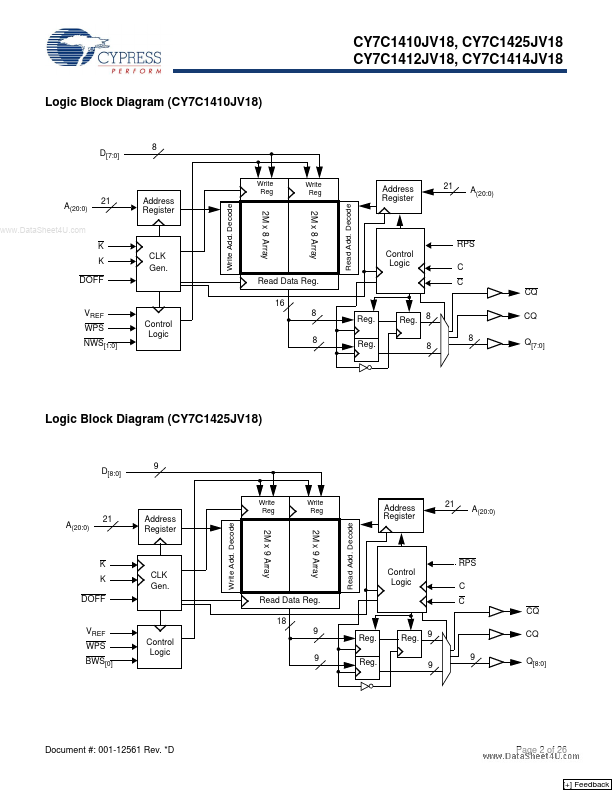

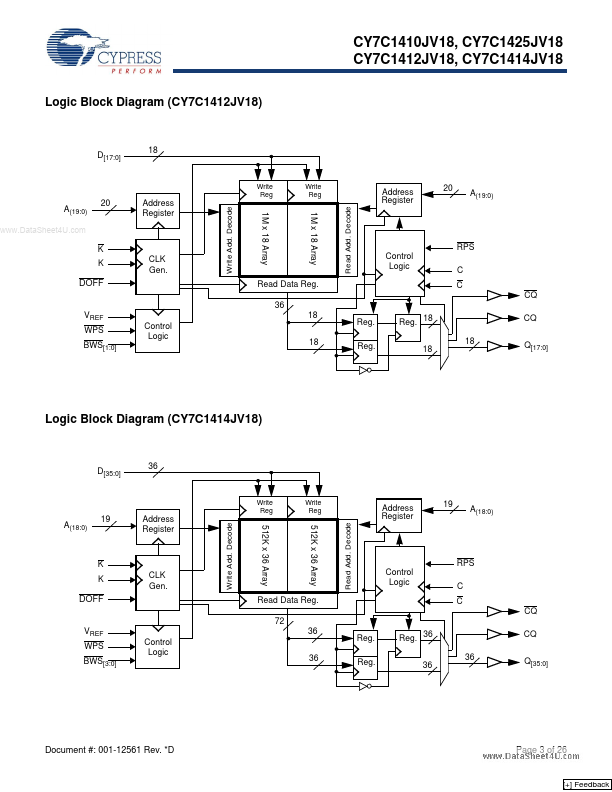

- Functional Description

The CY7C1410JV18, CY7C1425JV18, CY7C1412JV18, and CY7C1414JV18 are 1.8V Synchronous Pipelined SRAMs, equipped with QDR-II architecture. QDR-II architecture consists of two...