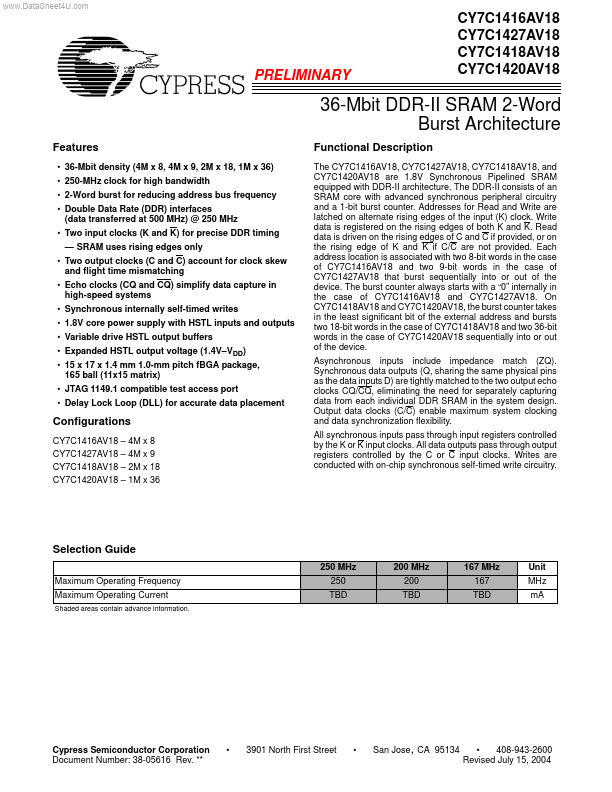

CY7C1416AV18

CY7C1416AV18 is 36-Mbit DDR-II SRAM 2-Word Burst Architecture manufactured by Cypress.

Features

- 36-Mbit density (4M x 8, 4M x 9, 2M x 18, 1M x 36)

- 250-MHz clock for high bandwidth

- 2-Word burst for reducing address bus frequency

- Double Data Rate (DDR) interfaces (data transferred at 500 MHz) @ 250 MHz

- Two input clocks (K and K) for precise DDR timing

- SRAM uses rising edges only

- Two output clocks (C and C) account for clock skew and flight time mismatching

- Echo clocks (CQ and CQ) simplify data capture in high-speed systems

- Synchronous internally self-timed writes

- 1.8V core power supply with HSTL inputs and outputs

- Variable drive HSTL output buffers

- Expanded HSTL output voltage (1.4V- VDD)

- 15 x 17 x 1.4 mm 1.0-mm pitch f BGA package, 165 ball (11x15 matrix)

- JTAG 1149.1 patible test access port

- Delay Lock Loop (DLL) for accurate data placement

Functional Description

The CY7C1416AV18, CY7C1427AV18, CY7C1418AV18, and CY7C1420AV18 are 1.8V Synchronous Pipelined SRAM equipped with DDR-II architecture. The DDR-II consists of an SRAM core with advanced synchronous peripheral circuitry and a 1-bit burst counter. Addresses for Read and Write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K and K. Read data is driven on the rising edges of C and C if provided, or on the rising edge of K and K if C/C are not provided. Each address location is associated with two 8-bit words in the case of CY7C1416AV18 and two 9-bit words in the case of CY7C1427AV18 that burst sequentially into or out of the device. The burst counter always starts with a “0” internally in the case of CY7C1416AV18 and CY7C1427AV18. On CY7C1418AV18 and CY7C1420AV18, the burst counter takes in the least significant bit of the external address and bursts two 18-bit words in the case of CY7C1418AV18 and two 36-bit words in the case of CY7C1420AV18 sequentially into or out of the device. Asynchronous inputs include impedance match (ZQ). Synchronous data outputs (Q, sharing the same physical pins as the data...