CY7C1475V25

CY7C1475V25 is (CY7C147xV25) 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM manufactured by Cypress.

- Part of the CY7C1471V25 comparator family.

- Part of the CY7C1471V25 comparator family.

..

PRELIMINARY

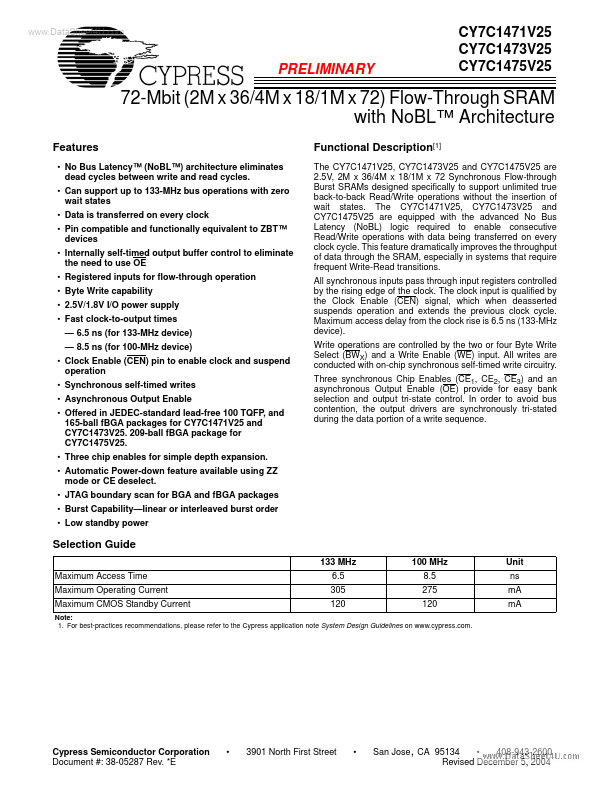

CY7C1471V25 CY7C1473V25 CY7C1475V25

72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL™ Architecture

Features

- No Bus Latency™ (NoBL™) architecture eliminates dead cycles between write and read cycles.

- Can support up to 133-MHz bus operations with zero wait states

- Data is transferred on every clock

- Pin patible and functionally equivalent to ZBT™ devices

- Internally self-timed output buffer control to eliminate the need to use OE

- Registered inputs for flow-through operation

- Byte Write capability

- 2.5V/1.8V I/O power supply

- Fast clock-to-output times

- 6.5 ns (for 133-MHz device)

- 8.5 ns (for 100-MHz device)

- Clock Enable...