Datasheet Summary

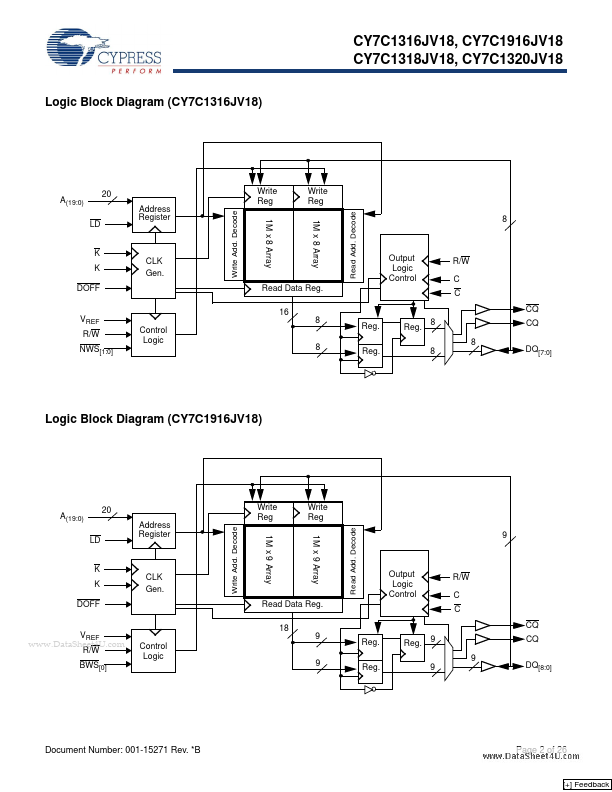

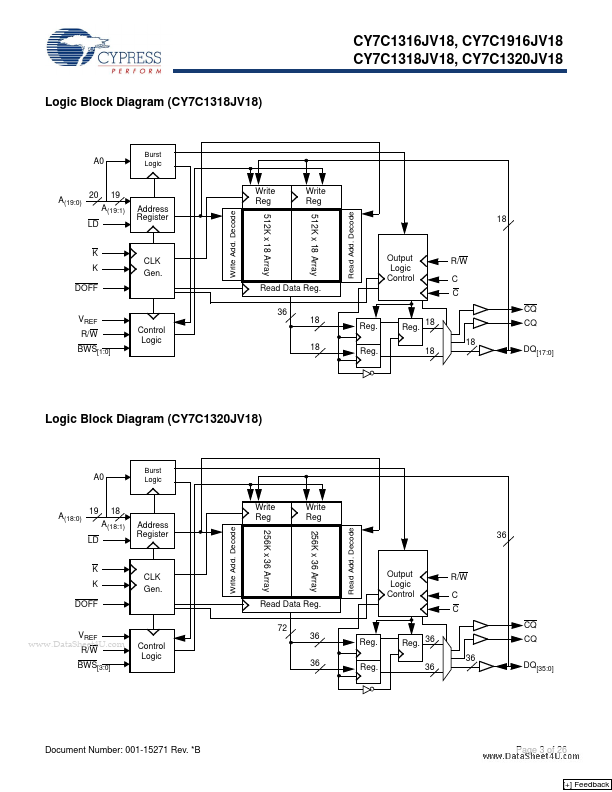

CY7C1316JV18, CY7C1916JV18 CY7C1318JV18, CY7C1320JV18

18-Mbit DDR-II SRAM 2-Word Burst Architecture

Features

- -

- -

- Functional Description

The CY7C1316JV18, CY7C1916JV18, CY7C1318JV18, and CY7C1320JV18 are 1.8V Synchronous Pipelined SRAMs equipped with DDR-II architecture. The DDR-II consists of an SRAM core with advanced synchronous peripheral circuitry and a one-bit burst counter. Addresses for read and write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K and K. Read data is driven on the rising edges of C and C if provided, or on the rising edge of K and K if C/C are not provided. Each address location is...