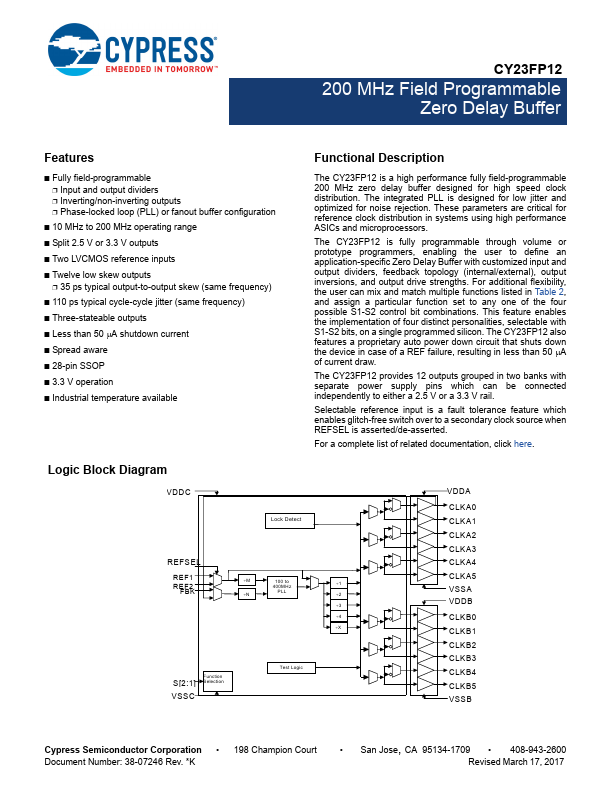

CY23FP12 Description

The CY23FP12 is a high performance fully field-programmable 200 MHz zero delay buffer designed for high speed clock distribution. The integrated PLL is designed for low jitter and optimized for noise rejection. These parameters are critical for reference clock distribution in systems using high performance ASICs.

CY23FP12 Key Features

- Fully field-programmable

- Input and output dividers

- Inverting/non-inverting outputs

- Phase-locked loop (PLL) or fanout buffer configuration

- 10 MHz to 200 MHz operating range

- Split 2.5 V or 3.3 V outputs

- Two LVCMOS reference inputs

- Twelve low skew outputs

- 35 ps typical output-to-output skew (same frequency)

- 110 ps typical cycle-cycle jitter (same frequency)