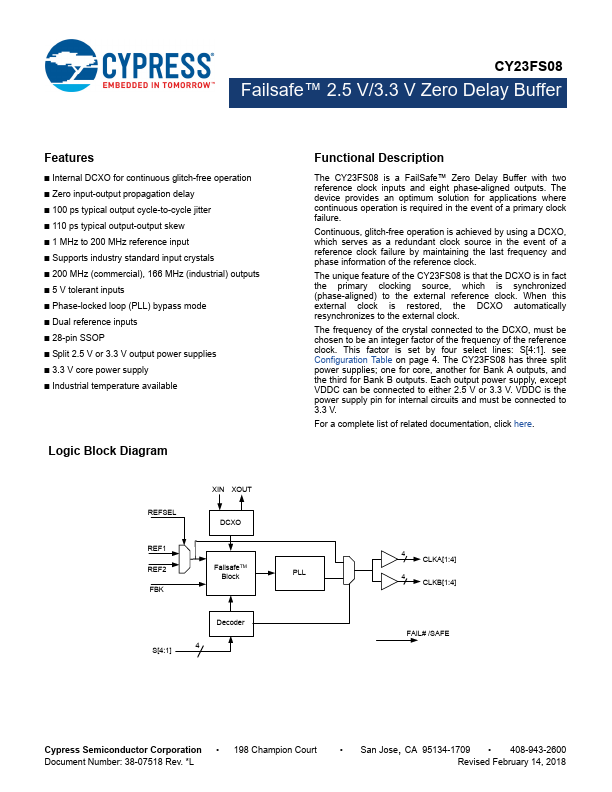

CY23FS08 Description

The CY23FS08 is a FailSafe™ Zero Delay Buffer with two reference clock inputs and eight phase-aligned outputs. The device provides an optimum solution for applications where continuous operation is required in the event of a primary clock.

CY23FS08 Key Features

- Internal DCXO for continuous glitch-free operation

- Zero input-output propagation delay

- 100 ps typical output cycle-to-cycle jitter

- 110 ps typical output-output skew

- 1 MHz to 200 MHz reference input

- Supports industry standard input crystals

- 200 MHz (mercial), 166 MHz (industrial) outputs

- 5 V tolerant inputs

- Phase-locked loop (PLL) bypass mode

- Dual reference inputs