CY62167GE Overview

Key Features

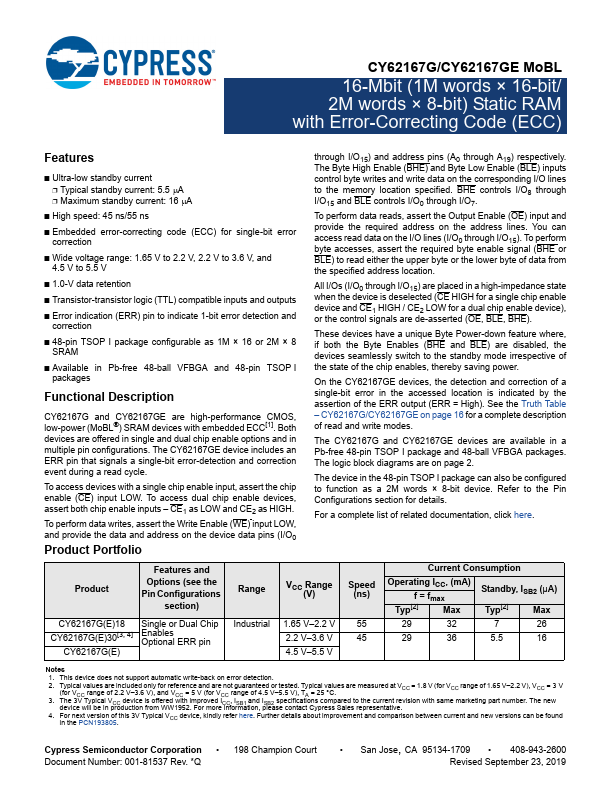

- Ultra-low standby current ❐ Typical standby current: 5.5 A ❐ Maximum standby current: 16 A

- High speed: 45 ns/55 ns

- Embedded error-correcting code (ECC) for single-bit error correction

- Wide voltage range: 1.65 V to 2.2 V, 2.2 V to 3.6 V, and 4.5 V to 5.5 V

- 1.0-V data retention

- Transistor-transistor logic (TTL) compatible inputs and outputs

- Error indication (ERR) pin to indicate 1-bit error detection and correction

- 48-pin TSOP I package configurable as 1M × 16 or 2M × 8 SRAM

- Available in Pb-free 48-ball VFBGA and 48-pin TSOP I packages