M14D5121632A-2.5BBG2A

M14D5121632A-2.5BBG2A is DDR-II SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

- Part of the M14D5121632A-1.5BG2A comparator family.

- Part of the M14D5121632A-1.5BG2A comparator family.

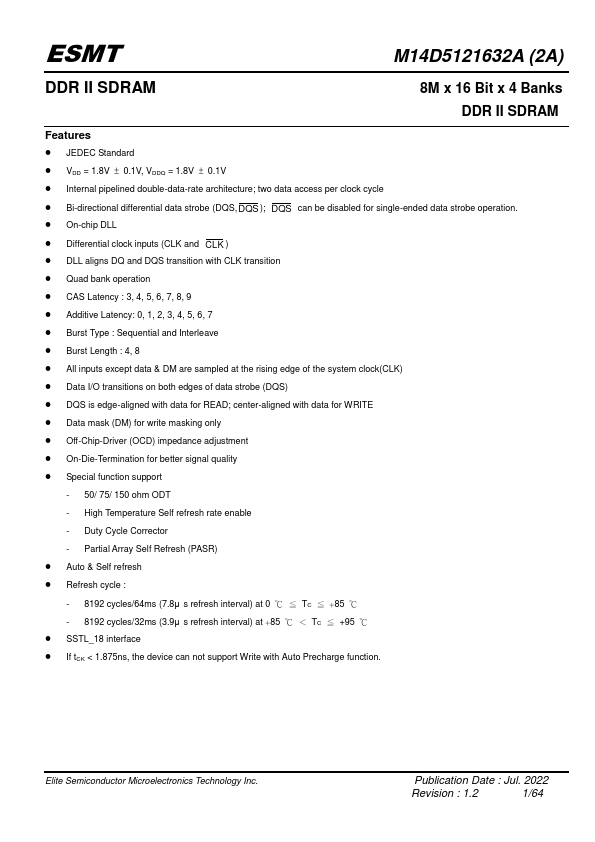

ESMT

M14D5121632A (2A)

DDR II SDRAM

8M x 16 Bit x 4 Banks DDR II SDRAM

Features

- JEDEC Standard

- VDD = 1.8V ± 0.1V, VDDQ = 1.8V ± 0.1V

- Internal pipelined double-data-rate architecture; two data access per clock cycle

- Bi-directional differential data strobe (DQS, DQS ); DQS can be disabled for single-ended data strobe operation.

- On-chip DLL

- Differential clock inputs (CLK and CLK )

- DLL aligns DQ and DQS transition with CLK transition

- Quad bank operation

- CAS Latency : 3, 4, 5, 6, 7, 8, 9

- Additive Latency: 0, 1, 2, 3, 4, 5, 6, 7

- Burst Type : Sequential and Interleave

- Burst Length : 4, 8

- All inputs except data & DM are sampled at the rising edge of the system...