M52D5123216A

M52D5123216A is 4M x 32 Bit x 4 Banks Mobile SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

FEATURES

- 1.8V power supply

- LVCMOS patible with multiplexed address

- Four banks operation

- MRS cycle with address key programs

- CAS Latency (2, 3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

- EMRS cycle with address

- All inputs are sampled at the positive going edge of the system clock

- Special function support

- PASR (Partial Array Self Refresh)

- TCSR (Temperature pensated Self Refresh)

- DS (Driver Strength)

- Deep Power Down (DPD) Mode

- DQM for masking

- Auto & self refresh

- 64ms refresh period (8K cycle)

4M x 32 Bit x 4 Banks

Mobile Synchronous DRAM

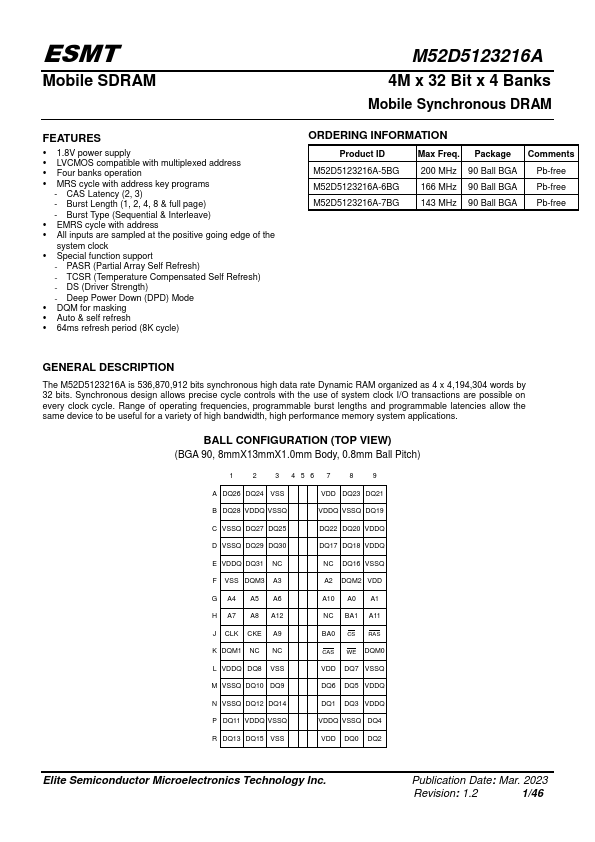

ORDERING INFORMATION

Product ID

Max Freq. Package ments

M52D5123216A-5BG M52D5123216A-6BG M52D5123216A-7BG

200 MHz 166 MHz 143 MHz

90 Ball BGA 90 Ball BGA 90 Ball BGA

Pb-free Pb-free Pb-free

GENERAL DESCRIPTION

The M52D5123216A is 536,870,912 bits synchronous high data rate Dynamic RAM organized as 4 x 4,194,304 words by 32 bits. Synchronous design allows precise cycle controls with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst lengths and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

BALL CONFIGURATION (TOP VIEW)

(BGA 90, 8mm X13mm X1.0mm Body, 0.8mm Ball Pitch)

3 456 7

A DQ26 DQ24 VSS

VDD DQ23 DQ21

B DQ28 VDDQ VSSQ

VDDQ VSSQ...