4X16E83VTW-6 Overview

Key Features

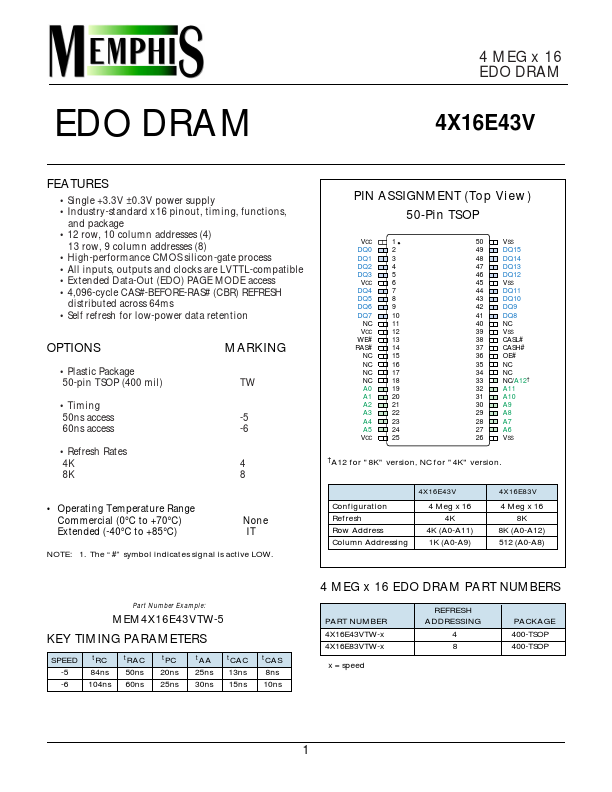

- Single +3.3V ±0.3V power supply

- Industry-standard x16 pinout, timing, functions, and package

- 12 row, 10 column addresses (4) 13 row, 9 column addresses (8)

- High-performance CMOS silicon-gate process

- All inputs, outputs and clocks are LVTTL-compatible