CH552

CH552 is 8 Enhanced USB single-chip manufactured by Unknown Manufacturer.

Overview

CH552 chip is a microcontroller core E8051 patible MCS51 enhanced instruction set that 79% of single-byte instructions are single cycle instructions, instruction average velocity MCS51 8 to 15 times faster than the standard.

CH552 system supports up to 32MHz frequency, built 16K bytes of program memory ROM and 256 bytes of internal i RAM 1K and the inner sheet x RAM, x RAM supports direct memory access DMA.

CH552 built ADC analog to digital converter, a capacitance detection touch key, group 3 and the PWM signal acquisition and timers, dual asynchronous serial interface, SPI, USB full-speed device controller and transceiver function modules.

CH551 to CH552 is a simplified version, only program memory ROM 10K, the sheet x RAM only 512 bytes, only asynchronous serial UART0 provided, only SOP16 package, and removes the ADC analog to digital conversion module and a USB type-C module in addition addition to the above difference with the same CH552, CH552 direct reference manuals and information.

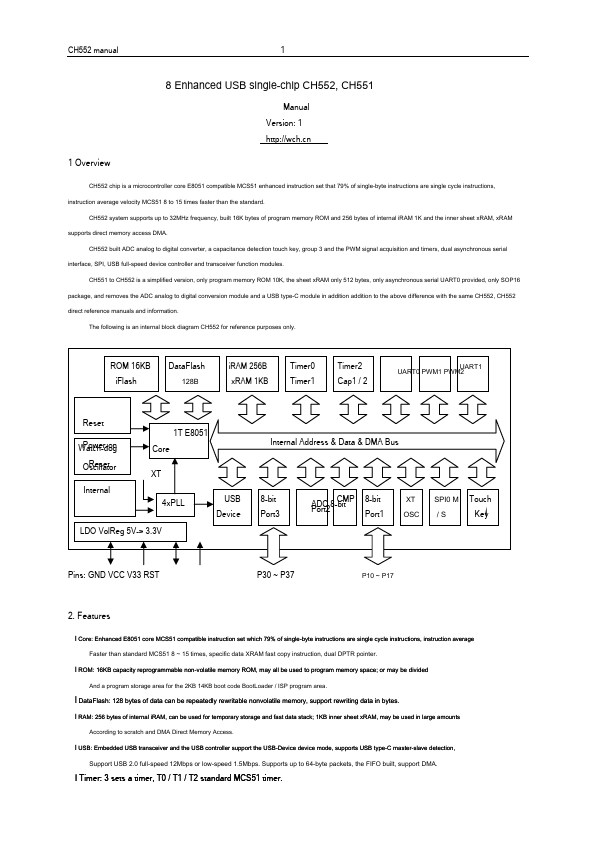

The following is an internal block diagram CH552 for reference purposes only.

ROM 16KB i Flash

Data Flash 128B i RAM 256B x RAM 1KB

Timer0 Timer1

Timer2 Cap1 / 2

UART1 UART0 PWM1 PWM2

Reset

Power-on Watch-dog

Reset Oscillator

1T E8051 Core

Internal

4x PLL

USB Device

LDO Vol Reg 5V-> 3.3V

Internal Address & Data & DMA Bus

8-bit Port3

CMP 8-bit ADC 8-bit Port2

Port1

XT OSC

SPI0 M Touch

/S

Key

Pins: GND VCC V33 RST

P30 ~ P37

P10 ~ P17

2. Features l Core: Enhanced E8051 core MCS51 patible instruction set which 79% of single-byte instructions are single cycle instructions, instruction average Faster than standard MCS51 8 ~ 15 times, specific data XRAM fast copy instruction, dual DPTR pointer. l ROM: 16KB capacity reprogrammable non-volatile memory ROM, may all be used to program memory space; or may be divided

And a program storage area for the 2KB 14KB boot code Boot Loader / ISP program area. l Data Flash: 128 bytes of data can be repeatedly rewritable...