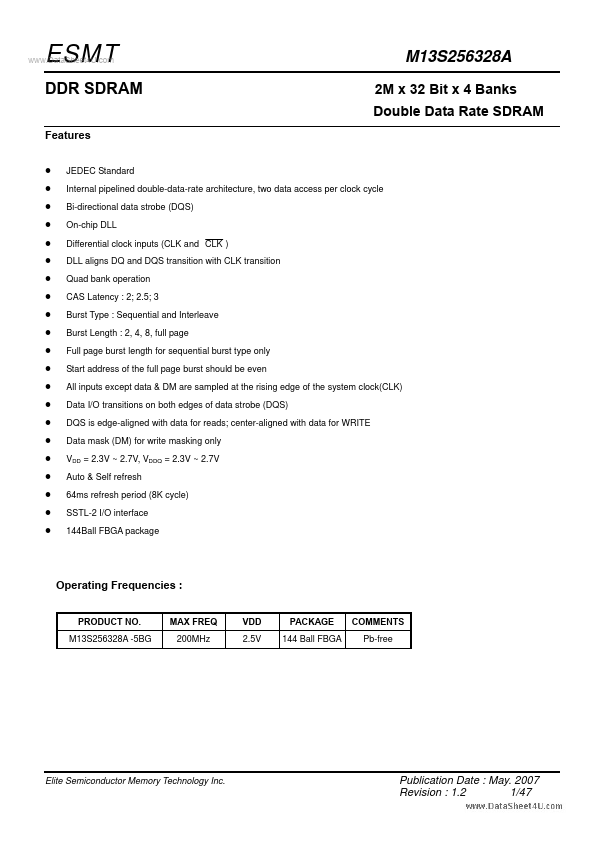

M13S256328A

M13S256328A is 2M x 32 Bit x 4 Banks Double Data Rate SDRAM manufactured by Elite Semiconductor Memory Technology.

..

ESMT

DDR SDRAM

Features z z z z z z z z z z z z z z z z z z z z z

2M x 32 Bit x 4 Banks Double Data Rate SDRAM

JEDEC Standard Internal pipelined double-data-rate architecture, two data access per clock cycle Bi-directional data strobe (DQS) On-chip DLL Differential clock inputs (CLK and CLK ) DLL aligns DQ and DQS transition with CLK transition Quad bank operation CAS Latency : 2; 2.5; 3 Burst Type : Sequential and Interleave Burst Length : 2, 4, 8, full page Full page burst length for sequential burst type only Start address of the full page burst should be even All inputs except data & DM are sampled at the rising edge of the system clock(CLK) Data I/O transitions on both edges of data strobe (DQS) DQS is edge-aligned with data for reads; center-aligned with data for WRITE Data mask (DM) for write masking only VDD = 2.3V ~ 2.7V, VDDQ = 2.3V ~ 2.7V Auto & Self refresh 64ms refresh period (8K cycle) SSTL-2 I/O interface 144Ball FBGA package

Operating Frequencies :

PRODUCT NO. M13S256328A -5BG MAX FREQ 200MHz VDD 2.5V PACKAGE 144 Ball FBGA MENTS Pb-free

Elite Semiconductor Memory Technology Inc.

Publication Date : May. 2007 Revision : 1.2 1/47

..

ESMT

Functional Block Diagram

CLK CLK CKE Address

Mode Register & Extended Mode Register

Clock Generator

Bank D Bank C Bank B Row Decoder Row Address Buffer & Refresh Counter

Bank A

Sense Amplifier mand Decoder Control Logic

CS RAS CAS WE

Data Control Circuit

Input & Output Buffer

Latch Circuit

Column Address Buffer & Refresh Counter

Column Decoder

CLK, CLK

Pin Arrangement

144(12x12) FBGA

2 B C D E F G H J K L M N DQS0 DQ4 DQ6 DQ7 DQ17 DQ19 DQS2 DQ21 DQ22 CAS RAS CS 3 DM0 VDDQ DQ5 VDDQ DQ16 DQ18 DM2 DQ20 DQ23 WE NC NC 4 VSSQ NC VSSQ VDD VDDQ VDDQ NC VDDQ VDDQ VDD NC BA0 5 DQ3 VDDQ VSSQ VSS VSSQ VSSQ VSSQ VSSQ VSSQ VSS BA1 A0 6 DQ2 DQ1 VSSQ VSSQ...