EBE11UD8AGUA

EBE11UD8AGUA is 1GB DDR2 SDRAM SO-DIMM manufactured by Elpida Memory.

DATA SHEET

..

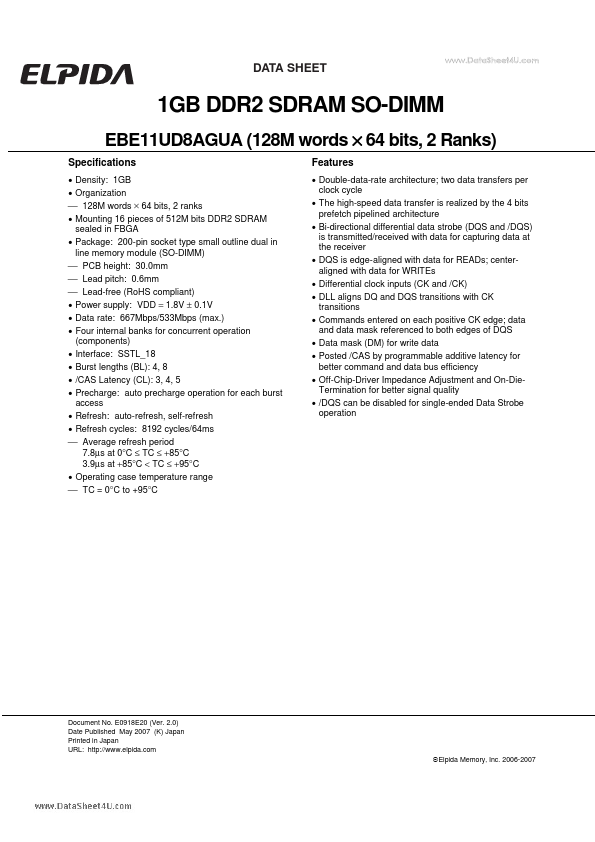

1GB DDR2 SDRAM SO-DIMM

EBE11UD8AGUA (128M words × 64 bits, 2 Ranks)

Specifications

- Density: 1GB

- Organization ⎯ 128M words × 64 bits, 2 ranks

- Mounting 16 pieces of 512M bits DDR2 SDRAM sealed in FBGA

- Package: 200-pin socket type small outline dual in line memory module (SO-DIMM) ⎯ PCB height: 30.0mm ⎯ Lead pitch: 0.6mm ⎯ Lead-free (Ro HS pliant)

- Power supply: VDD = 1.8V ± 0.1V

- Data rate: 667Mbps/533Mbps (max.)

- Four internal banks for concurrent operation (ponents)

- Interface: SSTL_18

- Burst lengths (BL): 4, 8

- /CAS Latency (CL): 3, 4, 5

- Precharge: auto precharge operation for each burst access

- Refresh: auto-refresh, self-refresh

- Refresh cycles: 8192 cycles/64ms ⎯ Average refresh period 7.8μs at 0°C ≤ TC ≤ +85°C 3.9μs at +85°C < TC ≤ +95°C

- Operating case temperature range ⎯ TC = 0°C to +95°C

Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

- Posted /CAS by programmable additive latency for better mand and data bus efficiency

- Off-Chip-Driver Impedance Adjustment and On-Die Termination for better signal...