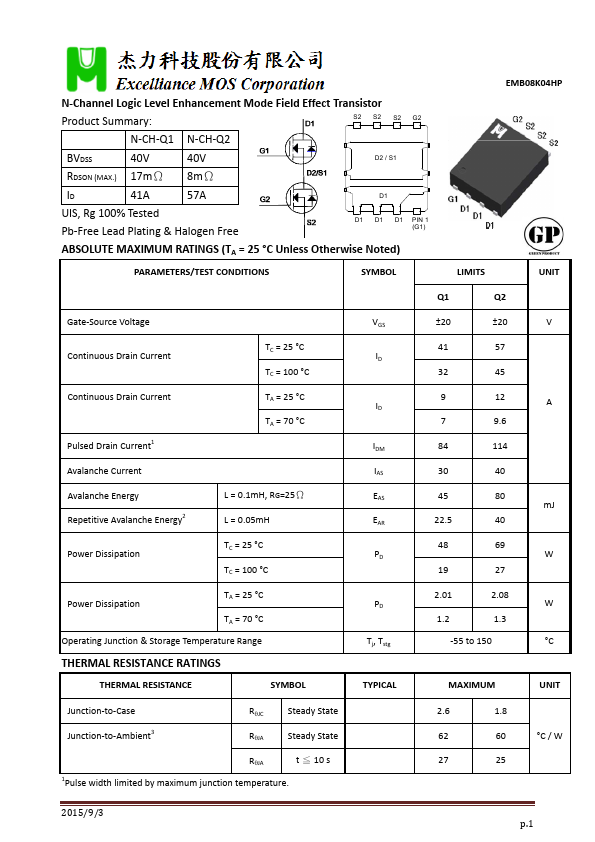

EMB08K04HP

EMB08K04HP is N-Channel Logic Level Enhancement Mode Field Effect Transistor manufactured by Excelliance MOS.

N‐Channel Logic Level Enhancement Mode Field Effect Transistor

Product Summary:

S2 S2 S2 G2

N‐CH‐Q1 N‐CH‐Q2

BVDSS

40V

40V

D2 / S1

RDSON (MAX.) 17mΩ 8mΩ

41A

57A

D1

UIS, Rg 100% Tested Pb‐Free Lead Plating & Halogen Free

D1 D1 D1 PIN 1 (G1)

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C Unless Otherwise Noted)

PARAMETERS/TEST CONDITIONS

SYMBOL

LIMITS

UNIT

Q1

Q2

Gate‐Source Voltage

Continuous Drain Current

TC = 25 °C TC = 100 °C

Continuous Drain Current

TA = 25 °C

Pulsed Drain Current1

TA = 70 °C

Avalanche Current

Avalanche Energy Repetitive Avalanche Energy2

L = 0.1m H, RG=25Ω L = 0.05m H

Power Dissipation

TC = 25 °C TC = 100 °C

Power Dissipation

TA = 25 °C TA = 70 °C

Operating Junction & Storage Temperature Range

THERMAL RESISTANCE RATINGS

THERMAL RESISTANCE

SYMBOL...