74LVTH322245

74LVTH322245 is Low Voltage 32-Bit Transceiver manufactured by Fairchild Semiconductor.

- Part of the 74LVT322245 comparator family.

- Part of the 74LVT322245 comparator family.

Description

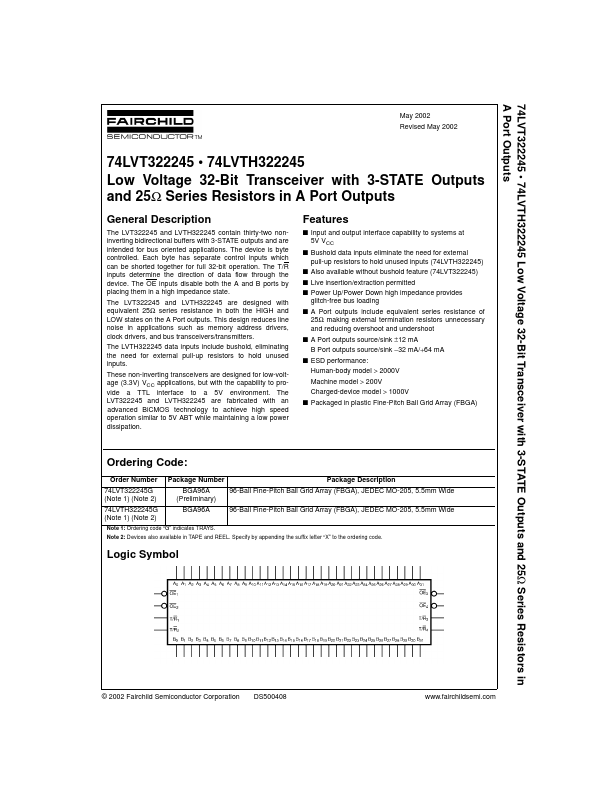

The LVT322245 and LVTH322245 contain thirty-two noninverting bidirectional buffers with 3-STATE outputs and are intended for bus oriented applications. The device is byte controlled. Each byte has separate control inputs which can be shorted together for full 32-bit operation. The T/R inputs determine the direction of data flow through the device. The OE inputs disable both the A and B ports by placing them in a high impedance state. The LVT322245 and LVTH322245 are designed with equivalent 25Ω series resistance in both the HIGH and LOW states on the A Port outputs. This design reduces line noise in applications such as memory address drivers, clock drivers, and bus transceivers/transmitters. The LVTH322245 data inputs include bushold, eliminating the need for external pull-up resistors to hold unused inputs. These non-inverting transceivers are designed for low-voltage (3.3V) VCC applications, but with the capability to provide a TTL interface to a 5V environment. The LVT322245 and LVTH322245 are fabricated with an advanced Bi CMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

Features s Input and output interface capability to systems at 5V VCC s Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH322245) s Also available without bushold feature

(74LVT322245) s Live insertion/extraction permitted s Power Up/Power Down high impedance provides glitch-free bus loading s A Port outputs include equivalent series resistance of 25Ω making external termination resistors unnecessary and reducing overshoot and undershoot s A Port outputs source/sink ±12 m A B Port outputs source/sink

- 32 m A/+64 m A s ESD performance: Human-body model > 2000V Machine model > 200V Charged-device model > 1000V s Packaged in plastic Fine-Pitch Ball Grid Array (FBGA)

Ordering Code:

Order Number 74LVT322245G (Note 1) (Note 2) 74LVTH322245G (Note 1) (Note 2) Package Number BGA96A...