GS81314PD19GK

GS81314PD19GK is 144Mb SigmaQuad-IVe Burst of 4 Single-Bank ECCRAM manufactured by GSI Technology.

- Part of the GS81314PD19GK-933 comparator family.

- Part of the GS81314PD19GK-933 comparator family.

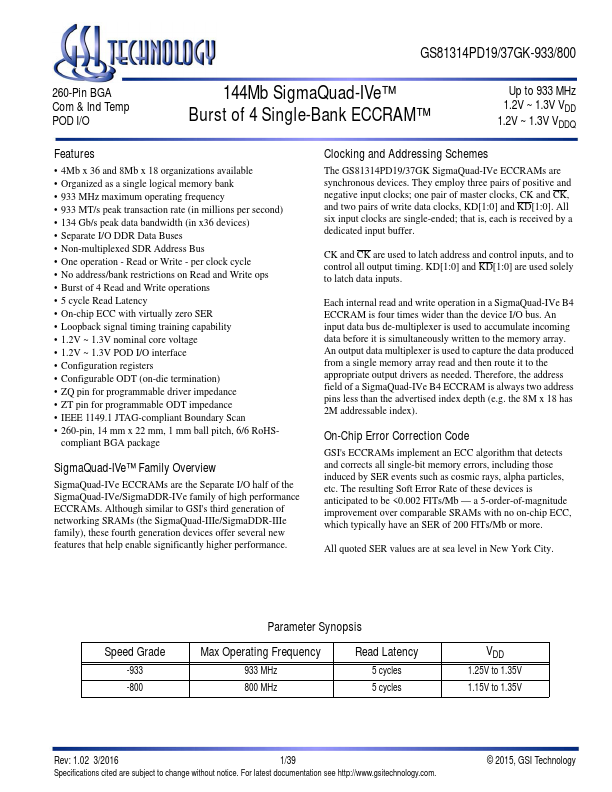

GS81314PD19/37GK-933/800

260-Pin BGA & Ind Temp POD I/O

144Mb Sigma Quad-IVe™ Burst of 4 Single-Bank ECCRAM™

Up to 933 MHz 1.2V ~ 1.3V VDD 1.2V ~ 1.3V VDDQ

Features

- 4Mb x 36 and 8Mb x 18 organizations available

- Organized as a single logical memory bank

- 933 MHz maximum operating frequency

- 933 MT/s peak transaction rate (in millions per second)

- 134 Gb/s peak data bandwidth (in x36 devices)

- Separate I/O DDR Data Buses

- Non-multiplexed SDR Address Bus

- One operation

- Read or Write

- per clock cycle

- No address/bank restrictions on Read and Write ops

- Burst of 4 Read and Write operations

- 5 cycle Read Latency

- On-chip ECC with virtually zero SER

- Loopback signal timing training capability

- 1.2V ~ 1.3V nominal core voltage

- 1.2V ~ 1.3V POD I/O interface

- Configuration registers

- Configurable ODT (on-die termination)

- ZQ pin for programmable driver impedance

- ZT pin for programmable ODT impedance

- IEEE 1149.1 JTAG-pliant Boundary Scan

- 260-pin, 14 mm x 22 mm, 1 mm ball pitch, 6/6 Ro HS- pliant BGA package

Sigma Quad-IVe™ Family Overview

Sigma Quad-IVe ECCRAMs are the Separate I/O half of the Sigma Quad-IVe/Sigma DDR-IVe family of high performance ECCRAMs. Although similar to GSI's third generation of networking SRAMs (the Sigma Quad-IIIe/Sigma DDR-IIIe family), these fourth generation devices offer several new Features that help enable significantly higher...