GS84118AB

GS84118AB is 256K x 18 Sync Cache Tag manufactured by GSI Technology.

- Part of the GS84118AT comparator family.

- Part of the GS84118AT comparator family.

..

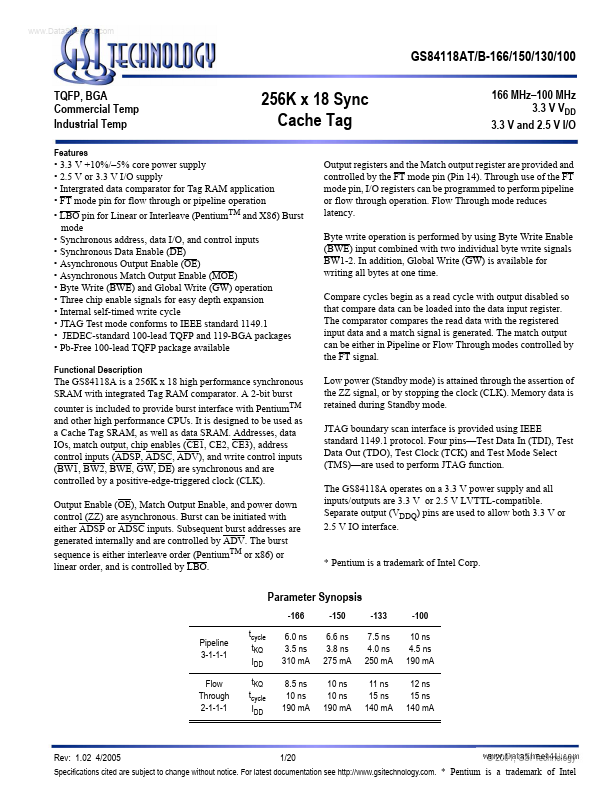

GS84118AT/B-166/150/130/100

TQFP, BGA mercial Temp Industrial Temp

256K x 18 Sync Cache Tag

166 MHz- 100 MHz 3.3 V VDD 3.3 V and 2.5 V I/O

Features

- 3.3 V +10%/- 5% core power supply

- 2.5 V or 3.3 V I/O supply

- Intergrated data parator for Tag RAM application

- FT mode pin for flow through or pipeline operation

- LBO pin for Linear or Interleave (Pentium TM and X86) Burst mode

- Synchronous address, data I/O, and control inputs

- Synchronous Data Enable (DE)

- Asynchronous Output Enable (OE)

- Asynchronous Match Output Enable (MOE)

- Byte Write (BWE) and Global Write (GW) operation

- Three chip enable signals for easy depth expansion

- Internal self-timed write cycle

- JTAG Test mode conforms to IEEE standard 1149.1

- JEDEC-standard 100-lead TQFP and 119-BGA packages

- Pb-Free 100-lead TQFP package available Functional Description The GS84118A is a 256K x 18 high performance synchronous SRAM with integrated Tag RAM parator. A 2-bit burst counter is included to provide burst interface with Pentium TM and other high performance CPUs. It is designed to be used as a Cache Tag SRAM, as well as data SRAM. Addresses, data IOs, match output, chip enables (CE1, CE2, CE3), address control inputs (ADSP, ADSC, ADV), and write control inputs (BW1, BW2, BWE, GW, DE) are synchronous and are controlled by a positive-edge-triggered clock (CLK). Output Enable (OE), Match Output Enable, and power down control (ZZ) are asynchronous. Burst can be initiated with either ADSP or ADSC inputs. Subsequent burst addresses are generated internally and are controlled by ADV. The burst sequence is either interleave order (Pentium TM or x86) or linear order, and is controlled by LBO.

Output registers and the Match output register are provided and controlled by the FT mode pin (Pin 14). Through use of the FT mode pin, I/O registers can be programmed to perform pipeline or flow through operation. Flow Through mode reduces latency. Byte write operation is performed...