HY57V161610D-I Key Features

- Single 3.0V to 3.6V power supplyNote1)

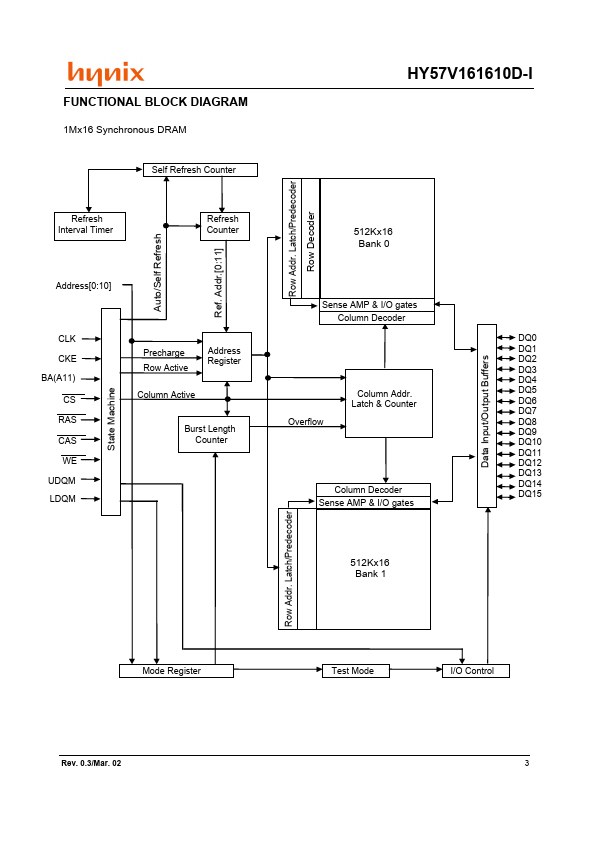

- Auto refresh and self refresh

- All device pins are patible with LVTTL interface

- 4096 refresh cycles / 64ms

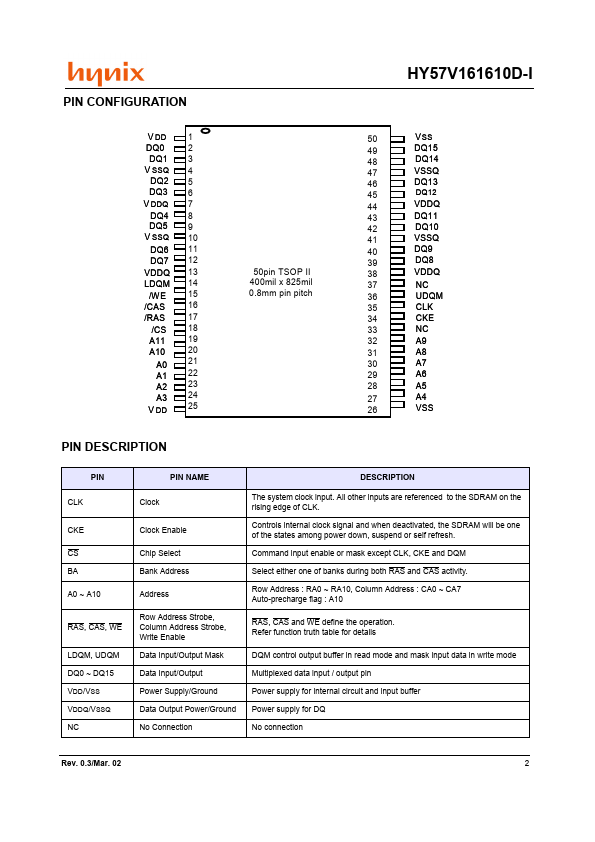

- JEDEC standard 400mil 50pin TSOP-II with 0.8mm of pin pitch

- All inputs and outputs referenced to positive edge of system clock

- Data mask function by UDQM/LDQM

- Programmable Burst Length and Burst Type

- 1, 2, 4, 8 and Full Page for Sequence Burst

- 1, 2, 4 and 8 for Interleave Burst