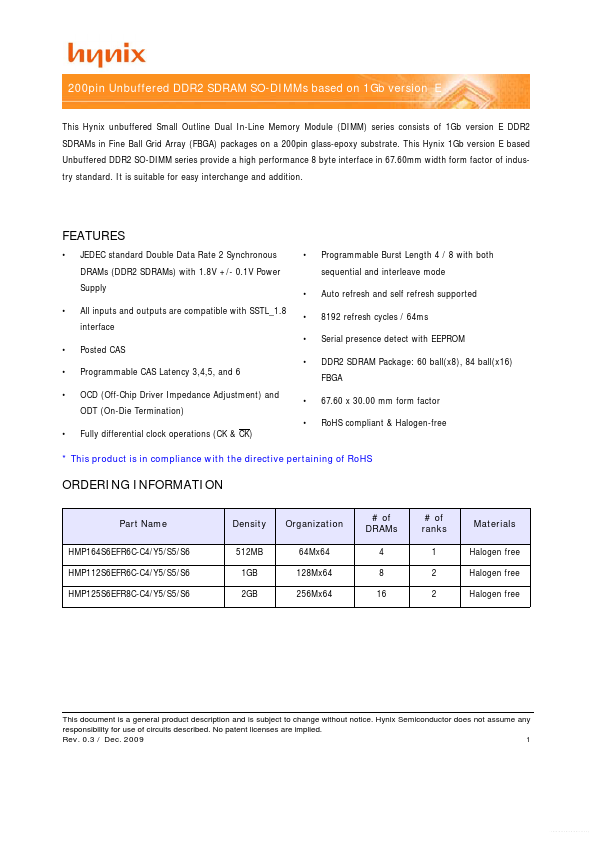

HMP112S6EFR6C-C4 Description

and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are implied.

HMP112S6EFR6C-C4 Key Features

- JEDEC standard Double Data Rate 2 Synchronous DRAMs (DDR2 SDRAMs) with 1.8V +/- 0.1V Power Supply

- All inputs and outputs are patible with SSTL_1.8 interface

- Posted CAS Programmable CAS Latency 3,4,5, and 6 OCD (Off-Chip Driver Impedance Adjustment) and ODT (On-Die Termination)

- Fully differential clock operations (CK & CK)

- 67.60 x 30.00 mm form factor RoHS pliant & Halogen-free

- This product is in pliance with the directive pertaining of RoHS