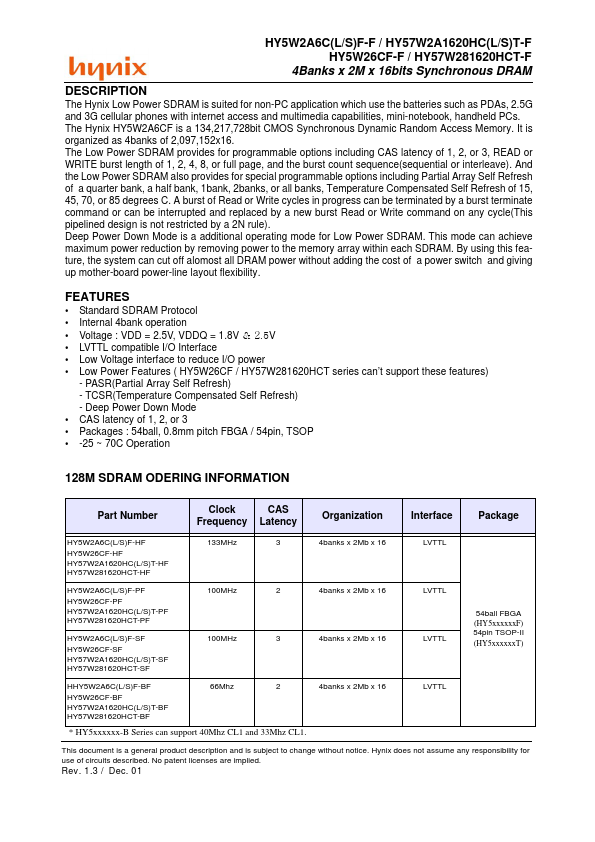

HY5W2A6C Key Features

- Standard SDRAM Protocol Internal 4bank operation Voltage : VDD = 2.5V, VDDQ = 1.8V & 2.5V LVTTL patible I/O Interface Lo

- PASR(Partial Array Self Refresh)

- TCSR(Temperature pensated Self Refresh)

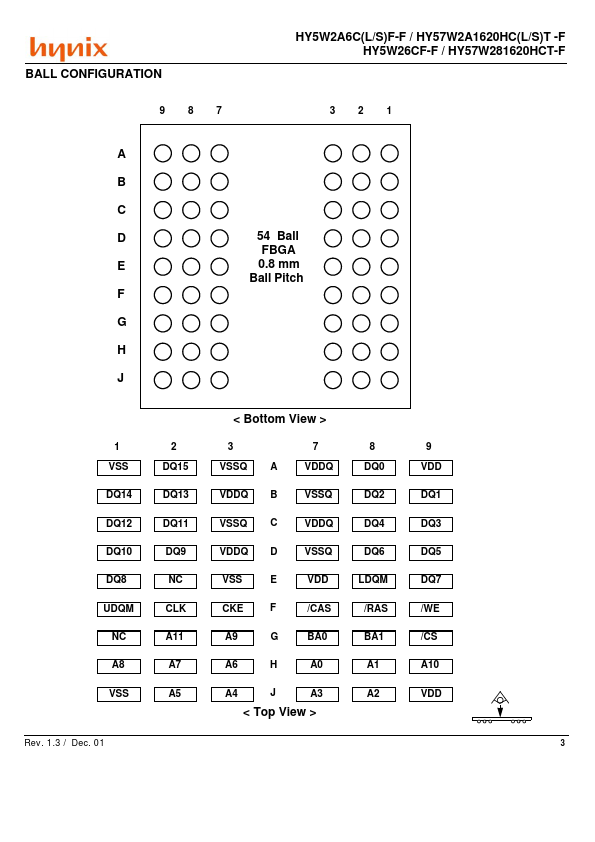

- Deep Power Down Mode CAS latency of 1, 2, or 3 Packages : 54ball, 0.8mm pitch FBGA / 54pin, TSOP -25 ~ 70C Opera