IS42S16400C

IS42S16400C is 64M-Bit x 16-Bit 4 4-Bank SDRAM manufactured by ISSI.

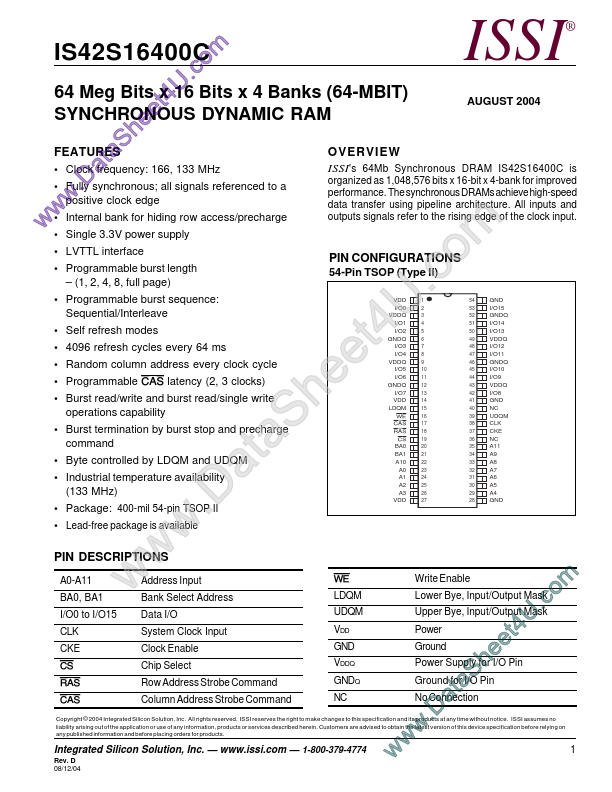

IS42S16400 .c U Bits x 4 Banks (64-MBIT) 64 Meg Bits x4 16 AUGUST 2004 t e SYNCHRONOUS DYNAMIC RAM e h S Features

OVERVIEW a t ISSI's 64Mb Synchronous DRAM IS42S16400C is

- Clock frequency: 166, 133 MHz a organized as 1,048,576 bits x 16-bit x 4-bank for improved D

- Fully . synchronous; all signals referenced to a performance. The synchronous DRAMs achieve high-speed positive w clock edge data transfer using pipeline architecture. All inputs and wInternal bank for hiding row access/precharge outputs signals refer to the rising edge of the clock input.

- w- Single 3.3V power supply

- LVTTL interface

- Programmable burst length

- (1, 2, 4, 8, full page)

- Programmable burst sequence:...